CDP1881CE Intersil Corporation, CDP1881CE Datasheet

CDP1881CE

Available stocks

Related parts for CDP1881CE

CDP1881CE Summary of contents

Page 1

... Functions Multiplexed or Non-Multiplexed • Decodes Up to 16K Bytes of Memory • Interfaces Directly with CDP1800-Series Microproces- sors at Maximum Clock Frequency • Can Replace CDP1866 and CDP1867 (Upward Speed and Function Capability) Ordering Information PACKAGE 5V 10V PDIP CDP1881CE - PDIP CDP1882CE - PDIP CDP1882CEX - Burn-In SBDIP - ...

Page 2

Absolute Maximum Ratings DC Supply Voltage Range (All Voltages Referenced to V Terminal) SS CDP1882 . . . . . . . . . . . . . . . . . . . . . . ...

Page 3

Static Electrical Specifications V O PARAMETER SYMBOL (V) Input Leakage Current I Any IN Input Operating Current DD1 (Note Input Capacitance Output Capacitance C - OUT Minimum Data V DR Retention ...

Page 4

INPUTS (NOTE 1) (NOTE 1) MWR MRD ...

Page 5

Dynamic Electrical Specifications PARAMETER PROPAGATION DELAY TIMES Chip Enable to Chip Select MRD or MRW to Chip Select (Note 3) CLOCK to Chip Select CLOCK to Address Memory Address to Chip Select Memory Address to Address NOTES Typical ...

Page 6

Signal Descriptions/Pin Functions CLOCK: Latch-Input Control - a high at the clock input will allow data to pass through the latch to the output pin. Data is latched on the high to low transition of the clock input. This input ...

Page 7

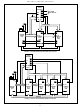

CDP1881C, CDP1882, CDP1882C WAIT CLR TPA CDP1800 ADDRESS BUS SERIES CPU MRD MWR FIGURE 5. CDP1800-SERIES SYSTEM USING THE CDP1882 CDP1882 LATCH/ DECODER CS3 CLK CS2 CS1 CE CS0 MA0 - MA5 A8 - A11 WAIT CLR A8 - A11 ...

Page 8

... All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification. Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use ...