SAA7392HL NXP Semiconductors, SAA7392HL Datasheet

SAA7392HL

Available stocks

Related parts for SAA7392HL

SAA7392HL Summary of contents

Page 1

DATA SHEET SAA7392 Channel encoder/decoder CDR60 Preliminary specification File under Integrated Circuits, IC01 INTEGRATED CIRCUITS 2000 Mar 21 ...

Page 2

Philips Semiconductors Channel encoder/decoder CDR60 CONTENTS 1 FEATURES 2 GENERAL DESCRIPTION 3 QUICK REFERENCE DATA 4 ORDERING INFORMATION 5 BLOCK DIAGRAM 6 PINNING INFORMATION 6.1 Pinning 6.2 Pin description 7 FUNCTIONAL DESCRIPTION 7.1 Microprocessor interfaces 7.2 Register map 7.3 System ...

Page 3

... ORDERING INFORMATION TYPE NUMBER NAME SAA7392HL LQFP80 plastic low profile quad flat package; 80 leads; body 12 2000 Mar 21 The bit detector recovers the individual bits from the incoming signal, correcting asymmetry, performing noise filtering and equalisation, and recovering the channel bit clock using a digital PLL ...

Page 4

Acrobat reader. white to force landscape pages to be ... WREFMID WIN WREFLO WREFHI ATIPSYC WOBBLE IREF IREF PROCESSOR ...

Page 5

Philips Semiconductors Channel encoder/decoder CDR60 6 PINNING INFORMATION 6.1 Pinning handbook, full pagewidth WREFLO 1 WREFHI 2 WREFMID 3 V SSA1 4 V DDA1 5 WIN 6 VREF 7 IREF 8 n.c. 9 HREFHI 10 HREFLO 11 AGCREF 12 HIN ...

Page 6

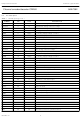

Philips Semiconductors Channel encoder/decoder CDR60 6.2 Pin description Table 1 LQFP80 package; note 1 SYMBOL PIN WREFLO 1 WREFHI 2 WREFMID SSA1 V 5 DDA1 WIN 6 VREF 7 IREF 8 n.c. 9 HREFHI 10 HREFLO 11 ...

Page 7

Philips Semiconductors Channel encoder/decoder CDR60 SYMBOL PIN DA3 39 DA2 40 DA1 41 DA0 DDE WRi 45 RDi 46 ALE 47 CSi 50 PCAin 51 STOPCK EBUOUT 56 SYNC 57 FLAG 58 DATAO 59 ...

Page 8

Philips Semiconductors Channel encoder/decoder CDR60 7 FUNCTIONAL DESCRIPTION 7.1 Microprocessor interfaces The SAA7392 is programmed via two independent microprocessor interfaces: 2 Serial I C-bus 2 – SDA = I C-bus data 2 – SCL = I C-bus clock 2 – ...

Page 9

Philips Semiconductors Channel encoder/decoder CDR60 handbook, full pagewidth ALE RDi CSi DA0 to DA7 Table 2 Parallel interface timing SYMBOL t Delay ALE falling to RDi/WRi falling Delay CSi rising to RDi/WRi falling CSi hold time ...

Page 10

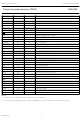

Acrobat reader. white to force landscape pages to be ... 7.2 Register map Table 3 Register map ADDRESS REGISTER NAME (HEX) 00 PLL Lock ...

Page 11

Acrobat reader. white to force landscape pages to be ... ADDRESS REGISTER NAME (HEX) 12 Clock Preset Register (ClockPre) 13 Decoder Mode Select Register ...

Page 12

Acrobat reader. white to force landscape pages to be ... ADDRESS REGISTER NAME (HEX) 2D ATIP Data End Register (ATIPDataEnd) 2E Wobble Peak Status ...

Page 13

Philips Semiconductors Channel encoder/decoder CDR60 7.2.1 I NTERRUPT PIN The interrupt pin (INT) is the AND-OR-INVERT of the Status and Interrupt Enable Registers, i.e. INT will become active when corresponding bits are set at the same time in the Status ...

Page 14

Philips Semiconductors Channel encoder/decoder CDR60 7.2 NTERRUPT NABLE EGISTER Table 9 Interrupt Enable Register (address 0BH) - WRITE 7 6 Sema1En Sema2En Sema3En Table 10 Description of IntEn bits BIT SYMBOL 7 Sema1En If Sema1En = 1, ...

Page 15

Philips Semiconductors Channel encoder/decoder CDR60 7.2 NTERRUPT NABLE EGISTER Table 13 Interrupt Enable Register 2 (address 21H) - WRITE 7 6 BankSwitch SyncErrorEn DataNotValid En Table 14 Description of IntEn2 bits BIT SYMBOL 7 BankSwitch If BankSwitchEn ...

Page 16

Philips Semiconductors Channel encoder/decoder CDR60 7.3 System clocks The principle clocks used in the SAA7392 are derived from the crystal oscillator input pin XTLI (alternatively, an external clock can be connected to this pin). These clocks are the system clock ...

Page 17

Philips Semiconductors Channel encoder/decoder CDR60 7.3 LOCK RESET EGISTER Table 17 Clock Preset Register (address 12H) - WRITE 7 6 CL1Div GateBClk Table 18 Description of ClockPre bits BIT SYMBOL 7 CL1Div If CL1Div = 0, then ...

Page 18

Philips Semiconductors Channel encoder/decoder CDR60 7.4 HF analog front-end The HF ADC in the SAA7392 encodes the EFM high frequency signal from the disc light pen assembly. These signals are pre-processed, externally to the SAA7392, by either AEGER ...

Page 19

Philips Semiconductors Channel encoder/decoder CDR60 7.5 Bit recovery The bit recovery block (shown in Fig.6) contains the slice level circuitry, a noise filter to limit the HF-EFM signal noise contribution, an adaptive slicer circuit and a digital PLL. These blocks ...

Page 20

Philips Semiconductors Channel encoder/decoder CDR60 7.5.1 D PLL IGITAL The digital PLL will recover the channel bit clock. As the capture range of the PLL itself is limited, lock detectors and 2 capture aids are present. In total three different ...

Page 21

Philips Semiconductors Channel encoder/decoder CDR60 7.5.2 MEAS1 PIN The MEAS1 pin carries the 3 measurement signals: jitter (sampled twice), PLL frequency, and asymmetry. Each frame consists of 64 bits (each 4 system clock periods long), beginning with a start bit, ...

Page 22

Philips Semiconductors Channel encoder/decoder CDR60 7.5.3 PLL OCK ELECT EGISTER The behaviour of this register is dependent upon whether its being read or written. The behaviour for the write operation is described in Tables 24 to 27. ...

Page 23

Philips Semiconductors Channel encoder/decoder CDR60 Table 28 Description of PLLock bits for read operation BIT SYMBOL PLLFreq<7:0> This register holds the 8 MSBs of the PLL frequency counter. The PLL frequency is calculated as shown below: f ...

Page 24

Philips Semiconductors Channel encoder/decoder CDR60 Table 33 Selection of PLL bandwidth PLLBWF1.1 PLLBWF1 21000 10528 5264 2632 Hz Table 34 Selection of low-pass bandwidth LPBWF2.1 LPBWF2 42100 ...

Page 25

Philips Semiconductors Channel encoder/decoder CDR60 7.5.6 PLL E P QUALIZER RESET The function of this register is dependent upon whether its being read or written. Tables 38, 39 and 40 define the register function for the write operation. Tables 38 ...

Page 26

Philips Semiconductors Channel encoder/decoder CDR60 7.5.7 PLL OCK ID RESET The PLL setting point for the EFM counting locking strategy is controlled by setting the PLL frequency such that, there are, on average, a fixed number ...

Page 27

Philips Semiconductors Channel encoder/decoder CDR60 7.5 ITERBI ETECTOR ETTING This register controls an advanced data slicer for improved bit detector performance. An adaptive slicer performs a second slice operation. This has a higher bandwidth than the first ...

Page 28

Philips Semiconductors Channel encoder/decoder CDR60 Table 48 Motor Control Register 1 (address 0CH) - READ 7 6 ASCV.7 ASCV.6 7.6 Decoder function 7.6.1 D EMODULATOR The demodulator block includes sync extraction, interpolation and protection circuits, and converts the 14-bit EFM ...

Page 29

Philips Semiconductors Channel encoder/decoder CDR60 7.6 ECODER ODE ELECT Table 50 Decoder Mode Select Register (address 13H) - WRITE 7 6 Mode.6 Mode.5 Table 51 Description of DecoMode bits BIT SYMBOL Mode<6:0> These 7 ...

Page 30

Philips Semiconductors Channel encoder/decoder CDR60 7.6.5 D FIFO ATA The decoder block can be viewed as a FIFO, demodulated data is written in while the output interface reads from it. The way in which the FIFO is filled depends on ...

Page 31

Philips Semiconductors Channel encoder/decoder CDR60 7.7 LOCK RESET EGISTER This is a dual-function register. When read the status of the Q-channel is returned. Table 55 Clock Preset Register (address 12H) - READ 7 6 Ready Busy Table ...

Page 32

Philips Semiconductors Channel encoder/decoder CDR60 7.8 Digital output The AES/EBU signal is available on pin EBUOUT, according to the format defined by the “IEC958 specification” . This signal is only available in the CLV modes of the decoder (not in ...

Page 33

Philips Semiconductors Channel encoder/decoder CDR60 7.8.2 F ORMAT The digital audio output consists of 32-bit words (subframes) transmitted in biphasemark code (two transitions for a logic 1 and one transition for a logic 0). Words are transmitted in blocks of ...

Page 34

Philips Semiconductors Channel encoder/decoder CDR60 7.9 Serial output interface The serial data output interface consists of three signals: WCLK (word select), BCLK (serial clock), DATAO (serial data). The polarity of WCLK and the data can be inverted. The FLAG signal ...

Page 35

Philips Semiconductors Channel encoder/decoder CDR60 handbook, full pagewidth BCLK DATA D15 D14 D13 D12 D11 D10 D9 FLAG FLAG - MSB (1 is unreliable) left WCLK SYNC handbook, full pagewidth BCLK DATA D1 D0 FLAG FLAG - MSB (1 is ...

Page 36

Acrobat reader. white to force landscape pages to be ... BCLK DATA D15 D14 D13 D12 D11 D10 FLAG FLAG - ...

Page 37

Philips Semiconductors Channel encoder/decoder CDR60 2 7.9 UTPUT EGISTER 2 Table Output Register 1 (address 05H) - WRITE 7 6 Format.2 Format.1 Table 64 Description of Output1 bits BIT SYMBOL 7 Format.2 ...

Page 38

Philips Semiconductors Channel encoder/decoder CDR60 2 7.9 UTPUT EGISTER 2 Table Output Register 3 (address 07H) - WRITE 7 6 WClkHLeft DescrmOn Table 69 Description of Output3 bits BIT SYMBOL 7 ...

Page 39

Philips Semiconductors Channel encoder/decoder CDR60 7.10 Motor control The spindle motor is controlled by a fully integrated digital servo sub-system within the SAA7392. Information from the data FIFO, data recovery PLL and tacho inputs may be used to calculate the ...

Page 40

Philips Semiconductors Channel encoder/decoder CDR60 7.10 OTOR ONTROL EGISTER The frequency/tacho set-point (i.e. the target PLL or tacho frequency) is calculated as follows: MFS<7:0> Frequency set-point 1 = – --------------------------- - PLLFreqR<7:0> PLL frequency = ----------------------------------------- - ...

Page 41

Philips Semiconductors Channel encoder/decoder CDR60 Table 74 Selection of coefficient K Ki 2.4 Table 75 Selection of the coefficient K Kf.2 Kf ...

Page 42

Philips Semiconductors Channel encoder/decoder CDR60 Table 78 Selection of coefficient K Kf’.2 Kf’.1 Ki’.2 Ki’. 7.10 OTOR ONTROL EGISTER The function ...

Page 43

Philips Semiconductors Channel encoder/decoder CDR60 7.10 OTOR ONTROL EGISTER Table 81 Motor Control Register (address 0FH) - WRITE 7 6 PWM_PDM OVF_SW Table 82 Description of Motor4 bits BIT SYMBOL 7 PWM_PDM If PWM_PDM = 0, then ...

Page 44

Philips Semiconductors Channel encoder/decoder CDR60 7.10 OTOR ONTROL EGISTERS These two registers hold the 16-bit motor integrator value. The motor integrator value can be read or updated using registers Motor5 and Motor6. Register Motor5 should be read ...

Page 45

Philips Semiconductors Channel encoder/decoder CDR60 7.10 ACHO ONTROL EGISTER Table 88 Tacho Control Register 3 (address 19H) - WRITE 7 6 SConS.1 SConS.0 TachoFRes Table 89 Description of Tacho3 bits BIT SYMBOL 7 SConS.1 These 2 bits ...

Page 46

Philips Semiconductors Channel encoder/decoder CDR60 7.11 The serial in function The serial in function takes serial data from the block decoder and passes the data on to the encoder. It supports the I and Sony 3-wire serial interfaces (DATAI, BCLK ...

Page 47

Philips Semiconductors Channel encoder/decoder CDR60 7.12 The subcode insert function The SAA7392 allows two modes of subcode insertion: Bypass mode and Auto-format mode. Bypass mode. In this mode the subcode is generated by a block decoder (such as PLUM) and ...

Page 48

Philips Semiconductors Channel encoder/decoder CDR60 7.12 UBCODE ONFIGURATION Table 96 Subcode Configuration Register 1 (address 23H) - WRITE 7 6 sri_on p_toggle Table 97 Description of SubConfig1 bits BIT SYMBOL 7 sri_on If sri_on = 0, then subcode ...

Page 49

Philips Semiconductors Channel encoder/decoder CDR60 7.12 UBCODE ONFIGURATION Table 99 Subcode Configuration Register 2 (address 24H) - READ/WRITE 7 6 BSwOn InOBO Table 100 Description of SubConfig2 bits BIT SYMBOL 7 BSwOn If BSwOn = 0, then no ...

Page 50

Philips Semiconductors Channel encoder/decoder CDR60 7.12.6 G CD-T ENERATING EXT CD-Text is stored in the channels of the disc. The CD-Text standard states that a CD-Text disc must at least contain CD-Text information in the lead-in, and ...

Page 51

Philips Semiconductors Channel encoder/decoder CDR60 7.14 NCODE TART FFSET Table 106 Encode Start Offset Register (address 31H) - WRITE 7 6 StartOffset.7 StartOffset.6 StartOffset.5 StartOffset.4 StartOffset.3 StartOffset.2 StartOffset.1 StartOffset.0 Table 107 Description of EncodeStartOffset bits BIT SYMBOL ...

Page 52

Philips Semiconductors Channel encoder/decoder CDR60 7.15 The EFM modulator This block takes data from the data encoder block and adds the subcode and synchronisation information. This data stream is modulated using EFM according to the Red Book standard. This data ...

Page 53

Philips Semiconductors Channel encoder/decoder CDR60 7.15.3 EFM M C ODULATOR ONFIGURATION Table 116 EFM Modulator Configuration Register 2 (address 3EH) - WRITE 7 6 Table 117 Description of EFMModConfig2 bits BIT SYMBOL These 5 bits are reserved. ...

Page 54

Philips Semiconductors Channel encoder/decoder CDR60 7.16 The EFM clock generator The EFM clock generator will produce the recording clock based on one of three reference sources. There are five stages to the function. The first selects the reference source using ...

Page 55

Philips Semiconductors Channel encoder/decoder CDR60 7.16.1 EFM C C LOCK ONFIGURATION Table 120 EFM Clock Configuration Register 1 (address 34H) - WRITE 7 6 DPLLBW.2 DPLLBW.1 DPLLBW.0 Table 121 Description of EFMClockConf1 bits BIT SYMBOL 7 DPLLBW.2 These 3 bits ...

Page 56

Philips Semiconductors Channel encoder/decoder CDR60 7.16.2 EFM C C LOCK ONFIGURATION Table 124 EFM Clock Configuration Register 2 (address 35H) - WRITE 7 6 FreqSrc.1 FreqSrc.0 Table 125 Description of EFMClockConf2 bits BIT SYMBOL 7 FreqSrc.1 These 2 bits select ...

Page 57

Philips Semiconductors Channel encoder/decoder CDR60 7.16.3 EFM C C LOCK ONFIGURATION This is a dual-function register, the specific function is controlled by the state of bit 7. The integrator of the PI controller can be preset by writing to this ...

Page 58

Philips Semiconductors Channel encoder/decoder CDR60 7.16.4 EFM C C LOCK ONFIGURATION (EFMC C F4) LOCK ON This is a dual-function register, the specific function is controlled by the state of bit 7. The sample rate of the integrator may be ...

Page 59

Philips Semiconductors Channel encoder/decoder CDR60 7.17 The Wobble processor The Wobble processor is a critical part of the recording process, and performs two main functions: To extract the ATIP data from the wobble signal To control the linear disc speed ...

Page 60

Philips Semiconductors Channel encoder/decoder CDR60 Table 137 Selection of integrator bandwidth PLLIntBW.2 PLLIntBW.1 PLLIntBW Table 138 Selection of loop bandwidth LOOPBW.2 LOOPBW.1 LOOPBW.0 0 ...

Page 61

Philips Semiconductors Channel encoder/decoder CDR60 7.17 OBBLE ONFIGURATION Table 140 Wobble Configuration Register 2 (address 28H) - WRITE 7 6 PLLLBW.2 Table 141 Description of WobbleConfig2 bits BIT SYMBOL 7 These 2 bits are reserved PLLLBW.2 ...

Page 62

Philips Semiconductors Channel encoder/decoder CDR60 7.17.7 ATIP S R TATUS EGISTER Table 143 ATIP Status Register (address 29H) - READ 7 6 ATIPReady Busy Table 144 Description of ATIPStatus bits BIT SYMBOL 7 ATIPReady If ATIPReady = 0, then ATIP ...

Page 63

Philips Semiconductors Channel encoder/decoder CDR60 7.17.10 ATIP D R (ATIPD ATA EGISTER The upper 16 bits of the ATIP data can be obtained from this register by carrying out consecutive read operations. Table 149 ATIP Data Register (address 2CH) - ...

Page 64

Philips Semiconductors Channel encoder/decoder CDR60 8 LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 60134). SYMBOL PARAMETER V supply voltage - pad output drivers DDE V supply voltage - core/pad ring DDD V supply voltage - analog ...

Page 65

Philips Semiconductors Channel encoder/decoder CDR60 9 OPERATING CHARACTERISTICS SYMBOL PARAMETER Supply V supply voltage (core/pad ring) DDD V supply voltage (analog) DDA V supply voltage (pad output drivers) DDE I supply current DD Digital inputs SCL (CMOS) V LOW-level input ...

Page 66

Philips Semiconductors Channel encoder/decoder CDR60 SYMBOL PARAMETER I 3-state leakage current LI C input capacitance i V LOW-level output voltage OL V HIGH-level output voltage OH C load capacitance L t output rise time r t output fall time f ...

Page 67

Philips Semiconductors Channel encoder/decoder CDR60 9.1 ADC and AGC parameters Table 156 ADC parameters PARAMETER VALUE Resolution 8-bit Data format Simple Binary Maximum sample 70 MS/s frequency SINAD >26 dB DNL 1.0/+1.0 LSB INL 2.0/+2.0 LSB Power dissipation <100 mW ...

Page 68

Philips Semiconductors Channel encoder/decoder CDR60 10 APPLICATION INFORMATION 10.1 Write start control of encoder in CD-ROM mode In CD-ROM mode, the CDR60 is intended to operate in lock-to-disc mode during write. When writing is stopped by the Encode Control Block, ...

Page 69

Philips Semiconductors Channel encoder/decoder CDR60 7. When the correct start address is found on the disc, the LaserOn and WriteOn2 signals are switched on at the same time result data flow in the encoder starts while data is ...

Page 70

Philips Semiconductors Channel encoder/decoder CDR60 11 PACKAGE OUTLINE LQFP80: plastic low profile quad flat package; 80 leads; body 1 pin 1 index DIMENSIONS (mm ...

Page 71

Philips Semiconductors Channel encoder/decoder CDR60 12 SOLDERING 12.1 Introduction to soldering surface mount packages This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our “Data Handbook IC26; ...

Page 72

Philips Semiconductors Channel encoder/decoder CDR60 12.5 Suitability of surface mount IC packages for wave and reflow soldering methods PACKAGE BGA, LFBGA, SQFP, TFBGA HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, SMS (3) PLCC , SO, SOJ LQFP, QFP, TQFP SSOP, TSSOP, ...

Page 73

Philips Semiconductors Channel encoder/decoder CDR60 13 DEFINITIONS Data sheet status Objective specification This data sheet contains target or goal specifications for product development. Preliminary specification This data sheet contains preliminary data; supplementary data may be published later. Product specification This ...

Page 74

Philips Semiconductors Channel encoder/decoder CDR60 2000 Mar 21 NOTES 74 Preliminary specification SAA7392 ...

Page 75

Philips Semiconductors Channel encoder/decoder CDR60 2000 Mar 21 NOTES 75 Preliminary specification SAA7392 ...

Page 76

Philips Semiconductors – a worldwide company Argentina: see South America Australia: 3 Figtree Drive, HOMEBUSH, NSW 2140, Tel. +61 2 9704 8141, Fax. +61 2 9704 8139 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. + 101 ...