74LVC2G32GM,125 NXP Semiconductors, 74LVC2G32GM,125 Datasheet

74LVC2G32GM,125

Specifications of 74LVC2G32GM,125

74LVC2G32GM-G

935277239125

Related parts for 74LVC2G32GM,125

74LVC2G32GM,125 Summary of contents

Page 1

Dual 2-input OR gate Rev. 06 — 27 February 2008 1. General description The 74LVC2G32 provides a 2-input OR gate function. Inputs can be driven from either 3 devices. This feature allows the use of ...

Page 2

... NXP Semiconductors 3. Ordering information Table 1. Ordering information Type number Package Temperature range Name 74LVC2G32DP +125 C 74LVC2G32DC +125 C 74LVC2G32GT +125 C 74LVC2G32GM +125 C 4. Marking Table 2. Marking codes Type number 74LVC2G32DP 74LVC2G32DC 74LVC2G32GT 74LVC2G32GM 5. Functional diagram 001aah791 Fig 1. Logic symbol Fig 3. Logic diagram (one gate) ...

Page 3

... NXP Semiconductors 6. Pinning information 6.1 Pinning Fig 4. Pin configuration TSSOP8 and VSSOP8 74LVC2G32 GND 4 Transparent top view Fig 5. Pin configuration XSON8 6.2 Pin description Table 3. Pin description Symbol Pin TSSOP8, VSSOP8 GND 74LVC2G32_6 Product data sheet 74LVC2G32 GND 4 001aab742 ...

Page 4

... NXP Semiconductors 7. Functional description [1] Table 4. Function table Input [ HIGH voltage level LOW voltage level. 8. Limiting values Table 5. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol Parameter V supply voltage CC V input voltage ...

Page 5

... NXP Semiconductors 9. Recommended operating conditions Table 6. Operating conditions Symbol Parameter V supply voltage CC V input voltage I V output voltage O T ambient temperature amb t/ V input transition rise and fall rate 10. Static characteristics Table 7. Static characteristics At recommended operating conditions; voltages are referenced to GND (ground = 0 V). ...

Page 6

... NXP Semiconductors Table 7. Static characteristics At recommended operating conditions; voltages are referenced to GND (ground = 0 V). Symbol Parameter I supply current CC I additional supply current CC C input capacitance +125 C amb V HIGH-level input voltage IH V LOW-level input voltage IL V HIGH-level output voltage LOW-level output voltage ...

Page 7

... NXP Semiconductors 11. Dynamic characteristics Table 8. Dynamic characteristics Voltages are referenced to GND (ground 0 V); for test circuit see Symbol Parameter Conditions t propagation delay nA nY; see power dissipation per gate capacitance [1] Typical values are measured at nominal V [ the same as t and PLH PHL [ used to determine the dynamic power dissipation (P ...

Page 8

... NXP Semiconductors Table 9. Measurement points Supply voltage 1. 2.7 V 2 3 5.5 V Test data is given in Table Definitions for test circuit Load resistor Load capacitance including jig and probe capacitance Termination resistance should be equal to output impedance Test voltage for switching times EXT Fig 8 ...

Page 9

... NXP Semiconductors 13. Package outline TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm; lead length 0 pin 1 index 1 e DIMENSIONS (mm are the original dimensions UNIT max. 0.15 0.95 mm 1.1 0.25 0.00 0.75 Note 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. ...

Page 10

... NXP Semiconductors VSSOP8: plastic very thin shrink small outline package; 8 leads; body width 2 pin 1 index 1 e DIMENSIONS (mm are the original dimensions UNIT max. 0.15 0. 0.12 0.00 0.60 Notes 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included. ...

Page 11

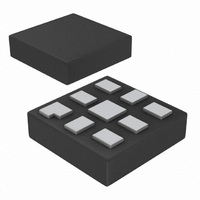

... NXP Semiconductors XSON8: plastic extremely thin small outline package; no leads; 8 terminals; body 1 x 1. (2) terminal 1 index area DIMENSIONS (mm are the original dimensions) ( UNIT b D max max 0.25 2.0 mm 0.5 0.04 0.17 1.9 Notes 1. Including plating thickness. 2. Can be visible in some manufacturing processes. ...

Page 12

... NXP Semiconductors XQFN8U: plastic extremely thin quad flat package; no leads; 8 terminals; UTLP based; body 1.6 x 1.6 x 0.5 mm terminal 1 index area metal area not for soldering 2 1 terminal 1 index area DIMENSIONS (mm are the original dimensions) A UNIT max 0.05 0.25 1.65 mm 0.5 0.00 ...

Page 13

... NXP Semiconductors 14. Abbreviations Table 11. Abbreviations Acronym Description CMOS Complementary Metal-Oxide Semiconductor DUT Device Under Test ESD ElectroStatic Discharge HBM Human Body Model MM Machine Model TTL Transistor-Transistor Logic 15. Revision history Table 12. Revision history Document ID Release date 74LVC2G32_6 20080227 • Modifications: Figure 1 • ...

Page 14

... Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice ...

Page 15

... NXP Semiconductors 18. Contents 1 General description . . . . . . . . . . . . . . . . . . . . . . 1 2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 3 Ordering information . . . . . . . . . . . . . . . . . . . . . 2 4 Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 5 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2 6 Pinning information . . . . . . . . . . . . . . . . . . . . . . 3 6.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 6.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3 7 Functional description . . . . . . . . . . . . . . . . . . . 4 8 Limiting values Recommended operating conditions Static characteristics Dynamic characteristics . . . . . . . . . . . . . . . . . . 7 12 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 13 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 9 14 Abbreviations ...