GM72V66841ELT-10K HYNIX [Hynix Semiconductor], GM72V66841ELT-10K Datasheet

GM72V66841ELT-10K

Related parts for GM72V66841ELT-10K

GM72V66841ELT-10K Summary of contents

Page 1

Description The GM72V66841ET/ELT is a synchronous dynamic random access memory comprised of 67,108,864 memory cells and logic including input and output circuits operating synchronously by referring to the positive edge of the externally provided Clock. The GM72V66841ET/ELT provides four banks ...

Page 2

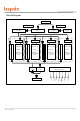

Block Diagram Column address counter Row decoder Memory array Bank 0 4096 row x 512 column x 8 bit Rev. 1.1/Apr. A13 Column address Row address buffer counter Row decoder Row decoder Memory array Memory ...

Page 3

Absolute Maximum Ratings Parameter Voltage on any pin relative to V Supply voltage relative Short circuit output current Power dissipation Operating temperature Storage temperature Notes : 1. Respect Recommended DC Operating Conditions (Ta ...

Page 4

DC Characteristics ( 70C, V Parameter Symbol Operating I CC1 current Standby current in I CC2P power down Standby current in power down I CC2PS (input signal stable) Standby current in non power down I CC2N (CAS ...

Page 5

DC Characteristics ( 70C, V (Continued) Parameter Symbol Input leakage current I LI Output leakage current I LO Output high voltage V OH Output low voltage V OL Notes : 1. I depends on output load condition ...

Page 6

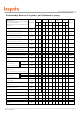

AC Characteristics ( 70C, V Parameter Symbol t (CL=2) System clock CK cycle time t (CL= CLK high pulse width CKH t CLK low pulse width CKL t (CL=2) Access time AC from CLK t ...

Page 7

AC Characteristics ( 70C, V (Continued) Parameter Symbol Write recovery or data-in t RWL to precharge lead time Active (a) to Active (b) t RRD command period t Refresh period REF Notes : 1. AC measurement assumes ...

Page 8

Relationship Between Frequency and Minimum Latency Parameter frequency(MHz) t (ns) CK Active command to column command (same bank) Active command to active command (same bank) Active command to Precharge command (same bank) Precharge command to active command (same bank) Write ...

Page 9

Relationship Between Frequency and Minimum Latency Parameter frequency(MHz) t (ns) CK Burst stop to (CL=2) output valid (CL=3) data hold Burst stop to (CL=2) output high (CL=3) impedance Burst stop to write data ignore Notes : ...

Page 10

Package Dimensions GM72V66841ET/ELT Series (TTP-54D) Preliminary 22.22 22.72 Max 54 1 0.80 +0.10 0.30 - 0.05 0.13 M 0.28 +/- 0.05 0.91 MAX 0.10 Dimension including the plating thickness Base material dimension Rev. 1.1/Apr. 11.76 +/- 0.20 Hitachi ...