PSD4235G2-90U STMicroelectronics, PSD4235G2-90U Datasheet - Page 64

PSD4235G2-90U

Manufacturer Part Number

PSD4235G2-90U

Description

IC FLASH 4MBIT 90NS 80TQFP

Manufacturer

STMicroelectronics

Datasheet

1.PSD4235G2-70U.pdf

(129 pages)

Specifications of PSD4235G2-90U

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

4M (512K x 8)

Speed

90ns

Interface

Parallel

Voltage - Supply

4.5 V ~ 5.5 V

Operating Temperature

0°C ~ 70°C

Package / Case

80-TQFP, 80-VQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-1968

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD4235G2-90U

Manufacturer:

MURATA

Quantity:

34 000

Company:

Part Number:

PSD4235G2-90U

Manufacturer:

STMicroelectronics

Quantity:

10 000

Part Number:

PSD4235G2-90U

Manufacturer:

ST

Quantity:

20 000

Company:

Part Number:

PSD4235G2-90UI

Manufacturer:

TI

Quantity:

8 802

Company:

Part Number:

PSD4235G2-90UI

Manufacturer:

STMicroelectronics

Quantity:

10 000

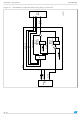

Complex PLD (CPLD)

18.3

18.4

18.5

64/129

Loading and Reading the output macrocells (OMC)

The output macrocells (OMC) block occupies a memory location in the MCU address space,

as defined by the CSIOP (see

macrocells (OMC) can be loaded from the data bus by a MCU. Loading the output

macrocells (OMC) with data from the MCU takes priority over internal functions. As such,

the preset, clear, and clock inputs to the flip-flop can be overridden by the MCU. The ability

to load the flip-flops and read them back is useful in such applications as loadable counters

and shift registers, mailboxes, and handshaking protocols.

Data is loaded to the output macrocells (OMC) on the trailing edge of Write Strobe

(WR/WRL, CNTL0).

The OMC Mask register

There is one Mask register for each of the two groups of eight output macrocells (OMC). The

Mask registers can be used to block the loading of data to individual output macrocells

(OMC). The default value for the Mask registers is 00h, which allows loading of the output

macrocells (OMC). When a given bit in a Mask register is set to a '1,' the MCU is blocked

from writing to the associated output macrocells (OMC). For example, suppose McellA0-

McellA3 are being used for a state machine. You would not want an MCU WRITE to McellA

to overwrite the state machine registers. Therefore, you would want to load the Mask

register for McellA (Mask macrocell A) with the value 0Fh.

The output Enable of the OMC

The output macrocells (OMC) can be connected to an I/O port pin as a PLD output. The

output enable of each port pin driver is controlled by a single product term from the AND

Array, ORed with the Direction register output. The pin is enabled upon Power-up if no

output enable equation is defined and if the pin is declared as a PLD output in PSDsoft

Express.

If the output macrocell (OMC) output is declared as an internal node and not as a port pin

output in the PSDabel file, then the port pin can be used for other I/O functions. The internal

node feedback can be routed as an input to the AND Array.

Section 20: I/O

ports). The flip-flops in each of the 16 output

PSD4235G2