OM11024 NXP Semiconductors, OM11024 Datasheet - Page 28

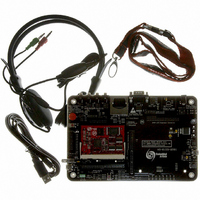

OM11024

Manufacturer Part Number

OM11024

Description

KIT EVAL FOR LPC313X

Manufacturer

NXP Semiconductors

Type

Microcontrollerr

Specifications of OM11024

Contents

2 Boards, cable and software

For Use With/related Products

LPC3131

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

568-4719

NXP Semiconductors

LPC3130_3131

Preliminary data sheet

6.20 Random number generator

6.21 Serial Peripheral Interface (SPI)

6.22 Universal Asynchronous Receiver Transmitter (UART)

The Random Number Generator (RNG) generates true random numbers for use in

advanced security and Digital Rights Management (DRM) related schemes. These

schemes rely upon truly random, i.e. completely unpredictable numbers.

This module has the following features:

The SPI module is used for synchronous serial data communication with other devices

which support the SPI/SSI protocol. Examples are memories, cameras, or WiFi-g.

The SPI/SSI-bus is a 5-wire interface, and it is suitable for low, medium, and high data

rate transfers.

This module has the following features:

The UART module supports the industry standard serial interface.

This module has the following features:

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

True random number generator.

The random number register does not rely on any kind of reset.

The generators are free running in order to ensure randomness and security.

Supports Motorola SPI frame format with a word size of 8/16 bits.

Texas Instruments SSI (Synchronous Serial Interface) frame format with a word size

of 4 bit to 16 bit.

Receive FIFO and transmit FIFO of 64 half-words each.

Serial clock rate master mode maximum 45 MHz.

Serial clock rate slave mode maximum 25 MHz.

Support for single data access DMA.

Full-duplex operation.

Supports up to three slaves.

Supports maskable interrupts.

Supports DMA transfers.

Programmable baud rate with a maximum of 1049 kBd.

Programmable data length (5 bit to 8 bit).

Implements only asynchronous UART.

Transmit break character length indication.

Programmable one to two stops bits in transmission.

Odd/Even/Force parity check/generation.

Frame error, overrun error and break detection.

Automatic hardware flow control.

Independent control of transmit, receive, line status, data set interrupts, and FIFOs.

All information provided in this document is subject to legal disclaimers.

Rev. 1.04 — 27 May 2010

Low-cost, low-power ARM926EJ-S microcontrollers

LPC3130/3131

© NXP B.V. 2010. All rights reserved.

28 of 72