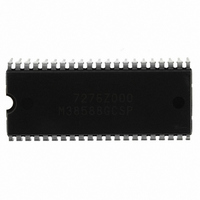

M38588GCSP#U0 Renesas Electronics America, M38588GCSP#U0 Datasheet - Page 29

M38588GCSP#U0

Manufacturer Part Number

M38588GCSP#U0

Description

IC 740/3858 MCU QZ-ROM 42DIP

Manufacturer

Renesas Electronics America

Series

740/38000r

Datasheet

1.M38588GCFPU0.pdf

(77 pages)

Specifications of M38588GCSP#U0

Core Processor

740

Core Size

8-Bit

Speed

12.5MHz

Connectivity

SIO, UART/USART

Peripherals

PWM, WDT

Number Of I /o

34

Program Memory Size

48KB (48K x 8)

Program Memory Type

QzROM

Ram Size

1.5K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 9x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

42-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

3858 Group

Timer Z1

The timer Z1 is a 16-bit timer. When the timer reaches “0000

an underflow occurs at the next count pulse and the correspond-

ing timer latch is reloaded into the timer and the count is

continued. When the timer underflows, the interrupt request bit

corresponding to the timer Z1 is set to “1”.

When reading/writing to the timer Z1, perform reading/writing to

both the high-order byte and the low-order byte. When reading the

timer Z1, read from the high-order byte first, followed by the low-

order byte. Do not perform the writing to the timer Z1 between

read operation of the high-order byte and read operation of the

low-order byte. When writing to the timer Z1, write to the low-order

byte first, followed by the high-order byte. Do not perform the

reading to the timer Z1 between write operation of the low-order

byte and write operation of the high-order byte.

The timer Z1 can select the count source by the timer Z1 count

source selection bits of timer Y, Z count source selection register

(bits 7 to 4 at address 000F

Timer Z1 can select one of seven operating modes by setting the

timer Z1 mode register (address 0028

(1) Timer mode

This mode can be selected by setting “000” to the timer Z1 operat-

ing mode bits (bits 2 to 0) and setting “0” to the timer/event

counter mode switch bit (b7) of the timer Z1 mode register (ad-

dress 0028

In high-, or middle-speed mode, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/

128, 1/256, 1/512 or 1/1024 of f(X

the count source.

In low-speed mode, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, 1/

512 or 1/1024 of f(X

source.

When an underflow occurs, the timer Z1/CNTR

bit (bit 0) of the interrupt request register 1 (address 003C

to “1”.

During timer stop, usually write data to a latch and a timer at the

same time to set the timer value.

The timer count operation is started by setting “0” to the timer Z1

count stop bit (bit 6) of the timer Z1 mode register (address

0028

When the timer reaches “0000

count pulse and the contents of timer latch are reloaded into the

timer and the count is continued.

When writing data to the timer during operation, the data is written

only into the latch. Then the new latch value is reloaded into the

timer at the next underflow.

REJ03B0139-0111

page 27 of 73

Mode selection

Count source selection

Interrupt

Explanation of operation

16-bit Timer

16

).

16

).

CIN

Rev.1.11

); or f(X

16

).

16

CIN

”, an underflow occurs at the next

IN

) can be selected as the count

); or f(X

Dec 18, 2008

16

).

CIN

) can be selected as

2

interrupt request

16

) is set

16

”,

(2) Event counter mode

This mode can be selected by setting “000” to the timer Z1 operat-

ing mode bits (bits 2 to 0) and setting “1” to the timer/event

counter mode switch bit (bit 7) of the timer Z1 mode register (ad-

dress 0028

The valid edge for the count operation depends on the CNTR

tive edge switch bit (bit 5) of the timer Z1 mode register (address

0028

falling edge is valid.

The interrupt at an underflow is the same as the timer mode’s.

The operation is the same as the timer mode’s.

Set the double-function port of CNTR

this mode.

Figure 22 shows the timing chart of the timer/event counter mode.

(3) Pulse output mode

This mode can be selected by setting “001” to the timer Z1 operat-

ing mode bits (bits 2 to 0) and setting “0” to the timer/event

counter mode switch bit (b7) of the timer Z1 mode register (ad-

dress 0028

In high-, or middle-speed mode, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/

128, 1/256, 1/512 or 1/1024 of f(X

the count source.

In low-speed mode, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, 1/

512 or 1/1024 of f(X

source.

The interrupt at an underflow is the same as the timer mode’s.

The operation is the same as the timer mode’s. Moreover the

pulse which is inverted each time the timer underflows is output

from CNTR

the timer Z1 mode register (address 0028

starts with “H” level. When it is “1”, the output starts with “L” level.

The double-function port of CNTR

cally set to the timer pulse output port in this mode.

The output from CNTR

CNTR

When the value of the CNTR

the output level of CNTR

Figure 23 shows the timing chart of the pulse output mode.

Precautions

Mode selection

Interrupt

Explanation of operation

Mode selection

Count source selection

Interrupt

Explanation of operation

16

2

). When it is “0”, the rising edge is valid. When it is “1”, the

active edge switch bit by writing to the timer.

16

16

2

pin. When the CNTR

).

).

CIN

2

); or f(X

pin is initialized to the level depending on

2

pin is inverted.

2

active edge switch bit is changed,

CIN

IN

2

2

) can be selected as the count

); or f(X

active edge switch bit (bit 5) of

pin and port P2

2

pin and port P2

CIN

16

) can be selected as

) is “0”, the output

2

is automati-

2

to input in

2

ac-