OM6274 NXP Semiconductors, OM6274 Datasheet - Page 9

OM6274

Manufacturer Part Number

OM6274

Description

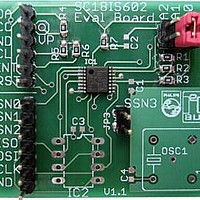

Interface Modules & Development Tools I2C to SPI Master Bridge Demoboard

Manufacturer

NXP Semiconductors

Datasheet

1.OM6274.pdf

(25 pages)

Specifications of OM6274

Interface Type

I2C, SPI

Data Bus Width

8 bit

For Use With/related Products

SC18IS602IPW

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

OM6274

Manufacturer:

NXP Semiconductors

Quantity:

135

NXP Semiconductors

SC18IS602_602B_603_4

Product data sheet

7.1.10 GPIO Enable - Function ID F6h

7.1.9 GPIO Read - Function ID F5h

The state of the pins defined as GPIO may be read into the SC18IS602/602B/603 data

buffer using the GPIO Read function.

Note that this function does not return the value of the GPIO. To receive the GPIO

contents, a one-byte Read Buffer command would be required. The value of the Read

Buffer command will return the following byte.

Table 7.

[1]

Data for pins not defined as GPIO are undefined.

A GPIO Read is always performed to update the GPIO data in the buffer. The buffer is

undefined after the GPIO data is read back from the buffer. Therefore, reading data from

the GPIO always requires a two-message sequence (GPIO Read, followed by Read

Buffer).

At reset, the Slave Select pins (SS0, SS1, SS2 and SS3) are configured to be used as

slave select outputs. If these pins are not required for the SPI functions, they can be used

as GPIO after they are enabled as GPIO. Any combination of pins may be configured to

function as GPIO or Slave Selects.

After the GPIO Enable function is sent, the ports defined as GPIO will be configured as

quasi-bidirectional.

The data byte following the F6h command byte will determine which pins can be used as

GPIO. A logic 1 will enable the pin as a GPIO, while a logic 0 will disable GPIO control.

Table 8.

[1]

Fig 14. GPIO Read

Fig 15. GPIO Enable

SS3 does not exist in the SC18IS603.

SS3 does not exist in the SC18IS603.

X

X

7

7

GPIO Read (F5h) bit allocation

GPIO Enable (F6h) bit allocation

X

X

6

6

S

S

SLAVE ADDRESS

SLAVE ADDRESS

Rev. 04 — 11 March 2008

X

X

5

5

W

W

X

X

4

4

A

A

SC18IS602/602B/603

F5h

F6h

SS3

SS3

3

3

[1]

[1]

A

A

DATA

DATA

SS2

SS2

2

2

002aac455

002aac456

I

2

A

A

C-bus to SPI bridge

P

P

SS1

SS1

© NXP B.V. 2008. All rights reserved.

1

1

SS0

SS0

0

0

9 of 25