IPR-FIR Altera, IPR-FIR Datasheet - Page 23

IPR-FIR

Manufacturer Part Number

IPR-FIR

Description

IP CORE Renewal Of IP-FIR

Manufacturer

Altera

Type

MegaCorer

Specifications of IPR-FIR

Software Application

IP CORE, DSP Filters And Transforms

Supported Families

Arria GX, Arria II GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Function

Finite Impulse Response Compiler

License

Renewal License

Lead Free Status / RoHS Status

na

Lead Free Status / RoHS Status

na

Chapter 2: Getting Started

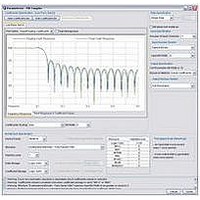

MegaWizard Plug-In Manager Flow

Compile the Design and Program a Device

© December 2010 Altera Corporation

f

f

Simulating in MATLAB

To simulate in a MATLAB environment, run the <variation_name>_model.m testbench

m-script, which also is located in your design directory. This script also uses the file

<variation name>_input.txt to provide input data. The output from the MATLAB

simulation is stored in the file <variation name>_model_output.txt.

For MCV decimation filters, the <variation name>_model_output_full.txt file is

generated to display all the phases of the filter. You can compare this file with the

<variation name>_output.txt file to understand which phase the output belongs. For

all other architectures, decimation filters provide the Nth phase where N is the

decimation factor.

Simulating in Third-Party Simulation Tools Using NativeLink

You can perform a simulation in a third-party simulation tool from within the

Quartus II software, using NativeLink.

The Tcl script file <variation name>_nativelink.tcl can be used to assign default

NativeLink testbench settings to the Quartus II project.

To perform a simulation in the Quartus II software using NativeLink, perform the

following steps:

1. Create a custom MegaCore function variation as described earlier in this chapter

2. Verify that the absolute path to your third-party EDA tool is set in the Options

3. On the Processing menu, point to Start and click Start Analysis & Elaboration.

4. On the Tools menu, click Tcl scripts. In the Tcl Scripts dialog box, select

5. On the Assignments menu, click Settings, expand EDA Tool Settings, and select

6. On the Tools menu, point to EDA Simulation Tool and click Run EDA RTL

For more information, refer to the

Quartus II Handbook.

You can use the Quartus II software to compile your design.

After you have compiled your design, program your targeted Altera device and

verify your design in hardware.

For instructions on compiling and programming your design, and more information

about the MegaWizard Plug-In Manager flow, refer to the Quartus II Help.

but ensure you specify your variation name to match the Quartus II project name.

page under the Tools menu in the Quartus II software.

<variation name>_nativelink.tcl and click Run. Check for a message confirming

that the Tcl script was successfully loaded.

Simulation. Select a simulator under Tool name then in NativeLink Settings,

select Compile test bench and click Test Benches.

Simulation.

The Quartus II software selects the simulator, and compiles the Altera libraries,

design files, and testbenches. The testbench runs and the waveform window

shows the design signals for analysis.

Simulating Altera Designs

chapter in volume 3 of the

FIR Compiler User Guide

2–9