CDB5566 Cirrus Logic Inc, CDB5566 Datasheet - Page 13

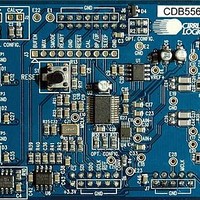

CDB5566

Manufacturer Part Number

CDB5566

Description

Dev Bd For I/C 24-bit, Diff, 5kSPS, DAQ

Manufacturer

Cirrus Logic Inc

Type

A/Dr

Specifications of CDB5566

Number Of Adc's

1

Number Of Bits

24

Sampling Rate (per Second)

5k

Data Interface

SPI™

Inputs Per Adc

2 Differential

Input Range

0 ~ 4.096 V

Power (typ) @ Conditions

20mW @ 5kSPS

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

CS5566

Conversion Rate

5 KSPS

Resolution

24 bit

Maximum Clock Frequency

8 MHz

Interface Type

SPI

Supply Voltage (max)

3.3 V

Supply Voltage (min)

- 2.5 V

Product

Data Conversion Development Tools

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS5566

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

598-1557

CDB-5566

CDB-5566

3/25/08

CS5566

2. OVERVIEW

The CS5566 is a 24-bit analog-to-digital converter capable of 5 kSps conversion rate. The device is ca-

pable of switching multiple input channels at a high rate with no loss in throughput. The ADC uses a

low-latency digital filter architecture. The filter is designed for fast settling and settles to full accuracy in

one conversion.

The converter is a serial output device. The serial port can be configured to function as either a master or

a slave.

The converter can operate from an analog supply of 5V or from ±2.5V. The digital interface supports stan-

dard logic operating from 1.8, 2.5, or 3.3 V.

The CS5566 converts at 5 kSps when operating from a 8 MHz input clock.

3. THEORY OF OPERATION

The CS5566 converter provides high-performance measurement of DC or AC signals. The converter can

be used to perform single conversions or continuous conversions upon command. Each conversion is in-

dependent of previous conversions and can settle to full specified accuracy, even with a full-scale input

voltage step. This is due to the converter architecture which uses a combination of a high-speed delta-sig-

ma modulator and a low-latency filter architecture.

Once power is established to the converter, a reset must be performed. A reset initializes the internal con-

verter logic.

If CONV is held low then the converter will convert continuously with RDY falling every 1600 MCLKs. This

is equivalent to 5 kSps if MCLK = 8.0 MHz. If CONV is tied to RDY, a conversion will occur every

1602 MCLKs. If CONV is operated asynchronously to MCLK, it may take up to 1604 MCLKs from CONV

falling to RDY falling.

Multiple converters can operate synchronously if they are driven by the same MCLK source and CONV

to each converter falls on the same MCLK falling edge. Alternately, CONV can be held low and all devices

are reset with RST rising on the same falling edge of MCLK.

The output coding of the conversion word is a function of the BP/UP pin.

The active-low SLEEP signal causes the device to enter a low-power state. When exiting sleep, the con-

verter will take 3083 MCLK cycles before conversions can be performed. RST should remain inactive

(high) when SLEEP is asserted (low).

DS806PP1

13