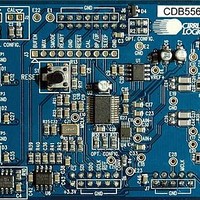

CDB5566 Cirrus Logic Inc, CDB5566 Datasheet - Page 20

CDB5566

Manufacturer Part Number

CDB5566

Description

Dev Bd For I/C 24-bit, Diff, 5kSPS, DAQ

Manufacturer

Cirrus Logic Inc

Type

A/Dr

Specifications of CDB5566

Number Of Adc's

1

Number Of Bits

24

Sampling Rate (per Second)

5k

Data Interface

SPI™

Inputs Per Adc

2 Differential

Input Range

0 ~ 4.096 V

Power (typ) @ Conditions

20mW @ 5kSPS

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

CS5566

Conversion Rate

5 KSPS

Resolution

24 bit

Maximum Clock Frequency

8 MHz

Interface Type

SPI

Supply Voltage (max)

3.3 V

Supply Voltage (min)

- 2.5 V

Product

Data Conversion Development Tools

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS5566

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

598-1557

CDB-5566

CDB-5566

3/25/08

CS5566

3.8 AIN & VREF Sampling Structures

The CS5566 uses on-chip buffers on the AIN+, AIN-, and the VREF+ inputs. Buffers provide much higher

input impedance and therefore reduce the amount of drive current required from an external source. This

helps minimize errors.

The Buffer Enable (BUFEN) pin determines if the on-chip buffers are used or not. If the BUFEN pin is con-

nected to the V1+ supply, the buffers will be enabled. If the BUFEN pin is connected to the V1- pin, the

buffers are off. The converter will consume about 5 mW less power when the buffers are off, but the input

impedances of AIN+, AIN- and VREF+ will be significantly less than with the buffers enabled.

3.9 Converter Performance

The CS5566 achieves excellent differential nonlinearity (DNL).

Figure 10

illustrates the code widths on

the typical scale of ±1 LSB and on a zoomed scale of ±0.2 LSB.

(Zoom View)

Figure 10. CS5566 DNL Plot

20

DS806PP1