CDB5566 Cirrus Logic Inc, CDB5566 Datasheet - Page 8

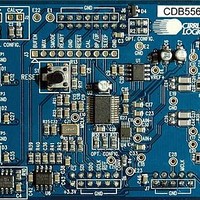

CDB5566

Manufacturer Part Number

CDB5566

Description

Dev Bd For I/C 24-bit, Diff, 5kSPS, DAQ

Manufacturer

Cirrus Logic Inc

Type

A/Dr

Specifications of CDB5566

Number Of Adc's

1

Number Of Bits

24

Sampling Rate (per Second)

5k

Data Interface

SPI™

Inputs Per Adc

2 Differential

Input Range

0 ~ 4.096 V

Power (typ) @ Conditions

20mW @ 5kSPS

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

CS5566

Conversion Rate

5 KSPS

Resolution

24 bit

Maximum Clock Frequency

8 MHz

Interface Type

SPI

Supply Voltage (max)

3.3 V

Supply Voltage (min)

- 2.5 V

Product

Data Conversion Development Tools

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS5566

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

598-1557

CDB-5566

CDB-5566

SWITCHING CHARACTERISTICS

T

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V Low; Logic 1 = VD+ = High; CL = 15 pF.

8

Serial Port Timing in SSC Mode (SMODE = VL)

Data hold time after SCLK rising

Serial Clock (Out)

(Note 13, 14)

RDY rising after last SCLK rising

CS falling to MSB stable

First SCLK rising after CS falling

CS hold time (low) after SCLK rising

SCLK, SDO tri-state after CS rising

SCLK(o)

A

MCLK

= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

SDO

RDY

CS

13. SDO and SCLK will be high impedance when CS is high. In some systems SCLK and SDO may require pull-down

14. SCLK = MCLK/2.

resistors.

Figure 3. SSC Mode - Read Timing, CS falling after RDY falls (Not to Scale)

t

11

Parameter

t

12

MSB

MSB–1

Pulse Width (high)

Pulse Width (low)

t

(CONTINUED)

7

3/25/08

t

Symbol

8

t

t

t

t

t

t

t

t

10

12

13

14

11

7

8

9

t

9

Min

100

100

10

-

-

-

-

-

LSB+1

t

13

LSB

Typ

10

10

8

8

5

-

-

-

t

14

t

10

Max

-

-

-

-

-

-

-

-

CS5566

DS806PP1

MCLKs

MCLKs

Unit

ns

ns

ns

ns

ns

ns