XC95108-15PC84I Xilinx Inc, XC95108-15PC84I Datasheet - Page 5

XC95108-15PC84I

Manufacturer Part Number

XC95108-15PC84I

Description

CPLD XC9500 Family 2.4K Gates 108 Macro Cells 55.6MHz 0.5um (CMOS) Technology 5V 84-Pin PLCC

Manufacturer

Xilinx Inc

Series

XC9500r

Specifications of XC95108-15PC84I

Package

84PLCC

Family Name

XC9500

Device System Gates

2400

Number Of Macro Cells

108

Maximum Propagation Delay Time

15 ns

Number Of User I/os

69

Number Of Logic Blocks/elements

8

Typical Operating Supply Voltage

5 V

Maximum Operating Frequency

55.6 MHz

Number Of Product Terms Per Macro

90

Memory Type

Flash

Operating Temperature

-40 to 85 °C

Programmable Type

In System Programmable (min 10K program/erase cycles)

Delay Time Tpd(1) Max

15.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

6

Number Of Macrocells

108

Number Of Gates

2400

Number Of I /o

69

Mounting Type

Surface Mount

Package / Case

84-PLCC

Voltage

5V

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Number Of Logic Elements/cells

-

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

122-1246

XC95108-15PC84I

XC95108-15PC84I

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC95108-15PC84I

Manufacturer:

XILINX

Quantity:

762

Company:

Part Number:

XC95108-15PC84I

Manufacturer:

XILINX

Quantity:

6 290

Part Number:

XC95108-15PC84I

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

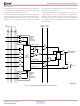

Macrocell

Each XC9500 macrocell may be individually configured for

a combinatorial or registered function. The macrocell and

associated FB logic is shown in

Five direct product terms from the AND-array are available

for use as primary data inputs (to the OR and XOR gates) to

implement combinatorial functions, or as control inputs

including clock, set/reset, and output enable. The product

DS063 (v5.5) June 25, 2007

Product Specification

36

R

Figure

Figure 3: XC9500 Macrocell Within Function Block

Allocator

Product

Term

3.

Additional

Product

Terms

(from other

macrocells)

Additional

Product

Terms

(from other

macrocells)

Product Term Clock

Product Term Reset

Product Term Set

Product Term OE

1

0

www.xilinx.com

Set/Reset

Global

term allocator associated with each macrocell selects how

the five direct terms are used.

The macrocell register can be configured as a D-type or

T-type flip-flop, or it may be bypassed for combinatorial

operation. Each register supports both asynchronous set

and reset operations. During power-up, all user registers

are initialized to the user-defined preload state (default to 0

if unspecified).

Clocks

3

Global

XC9500 In-System Programmable CPLD Family

D/T

R

S

Q

OUT

PTOE

To

Fast CONNECTII

Switch Matrix

DS063_03_110501

To

I/O Blocks

5