tc59ym916bkg24a ETC-unknow, tc59ym916bkg24a Datasheet - Page 58

tc59ym916bkg24a

Manufacturer Part Number

tc59ym916bkg24a

Description

The Second Generation 512-megabit Xdrtm Dram

Manufacturer

ETC-unknow

Datasheet

1.TC59YM916BKG24A.pdf

(76 pages)

DQN15…0

DQN15…0

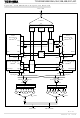

Simultaneous Precharge

addition to ERAW. This feature is simultaneous precharge, and the timing of several cases is shown in Figure 56.

with a single bank set, or between packets to the same bank set in a XDR DRAM with multiple bank sets. The

t

in a XDR DRAM with multiple bank sets.

precharge commands to different bank sets satisfy the same constraint as precharge commands to the same bank

set.

t

to a different bank set.

t

commands to a different bank set. In this case, the middle precharge command will not be symmetrically placed

relative to the two outer precharge commands.

t

possible by using the delay mechanism in one of the two commands. See “Dynamic Request Scheduling” on page 20.

It is also possible by taking advantage of the fact that two independent precharge commands may be encoded

within a single ROWP packet. In the example shown, the ROWP packet contains both a REFP command and a

PRE command. Both precharge commands will be issued internally to different bank sets on the same CFM clock

edge.

Figure 56. Simultaneous Precharge – t

PP-D

CYCLE

CYCLE

CYCLE

DQ15…0

DQ15…0

When the XDR DRAM supports multiple bank sets as in Figure 55, another feature may be supported, in

The t

In Figure 56, Case 4 shows an example when both t

In Figure 56, Case 2 shows an example when t

In Figure 56, Case 1 shows an example when t

In Figure 56, Case 0 shows an example when t

RQ11

RQ11

…RQ0

…RQ0

CFMN

CFMN

CFM

CFM

parameter specifies the minimum spacing between packets with precharge commands to different bank sets

PP

. In such a case, a precharge command to one bank set may be inserted between two precharge commands

. As in the previous case, a precharge command to one bank set may be inserted between two precharge

. This means that two precharge commands may be issued on the same CFM clock edge. This is only

T

T

PRE

PRE

0

0

parameter specifies the minimum spacing between packets with precharge commands in XDR DRAMs

t

PP-D

T

T

REFP

1

1

Case 1: t

REFP fits between two PRE

t

PP-D

T

T

t

2

2

PP

T

T

PP-D

3

3

= 1*t

T

REFP

T

PRE

4

4

Note – REFP is directed to bank

set different from two PRE

Case 4: t

REFP & PRE have same t

CYCLE

T

T

5

5

t

PP-D

T

T

PP-D

6

6

T

T

= 4*t

7

7

CYCLE

T

T

PRE

8

8

T

T

PP

PP

PP

RR.

TC59YM916BKG24A,32A,32B,40B,32C,40C

9

9

must be at least 4 × t

must be at least 4 × t

must be at least 4 × t

T

T

10

10

PP

PP-D

T

T

and t

t

PP-D

11

11

T

T

Cases

REFP

PRE

PRE

PP-D

12

12

Case 0: t

REFP simultaneous with PRE

t

PP-D

T

T

13

13

must be at least 4 × t

T

T

t

t

REFP

PP

PP-D

PP

14

14

Case 2: t

REFP fits between two PRE

CYCLE

CYCLE

CYCLE

T

T

= 0*t

15

15

CYCLE

T

T

PRE

PRE

PP-D

16

16

and t

and t

and t

Note – REFP is directed to bank

set different from PRE at T

T

T

= 2*t

17

17

Note – REFP is directed to bank

set different from two PRE

PP-D

PP-D

PP-D

CYCLE

T

T

18

18

CYCLE

must be at least 2 ×

must be at least 1 ×

must be at least 0 ×

2004-12-15 58/76

T

T

19

19

. In such a case,

T

T

20

20

T

T

21

21

12

Rev 0.1

T

T

t

t

CYCLE

CYCLE

22

22

T

T

23

23