SAA7113 Philips Semiconductors, SAA7113 Datasheet - Page 64

SAA7113

Manufacturer Part Number

SAA7113

Description

9-bit video input processor

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7113.pdf

(80 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

SAA7113

Manufacturer:

台湾明智类比

Quantity:

20 000

Part Number:

SAA7113H

Manufacturer:

PHILIPS

Quantity:

20 000

Company:

Part Number:

SAA7113H/V2

Manufacturer:

NXP

Quantity:

12 000

Part Number:

SAA7113H/V2

Manufacturer:

NXP/恩智浦

Quantity:

20 000

Company:

Part Number:

SAA7113H/V2,518

Manufacturer:

Sigma Designs Inc

Quantity:

10 000

Philips Semiconductors

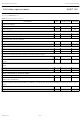

Table 50 RTS1 output control SA 12

1999 Jul 01

3-state, pin RTS1 is used as DOT input; see Table 19

VIPB (subaddress 11H bit 1) = 0: reserved

VIPB (subaddress 11H bit 1) = 1: LSBs of the 9-bit ADCs

GPSW1

HL (horizontal lock indicator); selectable via HLSEL (subaddress 11H, bit 4)

VL (vertical and horizontal lock)

DL (vertical and horizontal lock and colour detected)

PLIN (PAL/SECAM sequence; LOW: PAL/DR line is present)

HREF_HS, horizontal reference signal: indicates valid data on the

VPO-bus. The positive slope marks the beginning of a new active line.

The pulse width is dependent on the data type selected by the control

registers LCR2 to LCR24 (subaddress 41H to 57H; see Tables 4 and 61)

HS, programmable width in LLC8 steps via HSB7 to HSB0 and

HSS7 to HSS0 (subaddress 06H and 07H), fine position adjustment in

LLC2 steps via HDEL1 to HDEL0 (subaddress 10H, bits 5 and 4)

HQ (HREF gated with VREF)

ODD, field identifier; HIGH = odd field; see vertical timing diagrams

Figs 29 and 30

VS (vertical sync); see vertical timing diagrams Figs 29 and 30

V123 (vertical pulse); see vertical timing diagrams Figs 29 and 30

VGATE (programmable via VSTA8 to VSTA0 and VSTO8 to VSTO0,

subaddresses 15H, 16H and 17H)

VREF (programmable in two positions via VRLN, subaddress 10H, bit 3)

FID (position and polarity programmable via VSTA 8 to VSTA0,

subaddresses 15H and 17H and FIDP, subaddress 13 bit 3)

9-bit video input processor

HLSEL = 0: standard horizontal lock indicator

HLSEL = 1: fast horizontal lock indicator (use is not recommended for

sources with unstable timebase e. g. VCRs)

data type 0 to 6, 8 to 15: HIGH period 1440 LLC-cycles (720 samples;

see Fig.28)

data type 7 (upsampled raw data): HIGH period programmable in LLC8

steps via HSB7 to HSB0, HSS7 to HSS0 (subaddress 06H and 07H), fine

position adjustment via HDEL1 to HDEL0 (subaddress 10H, bits 5 and 4)

RTS1 OUTPUT CONTROL

64

RTSE13 RTSE12 RTSE11 RTSE10

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

D7 TO D4

Product specification

SAA7113H

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1