PALCE20V8H-25PC/4 Lattice Semiconductor, PALCE20V8H-25PC/4 Datasheet - Page 5

PALCE20V8H-25PC/4

Manufacturer Part Number

PALCE20V8H-25PC/4

Description

EE CMOS 24-Pin Universal Programmable Array Logic

Manufacturer

Lattice Semiconductor

Datasheet

1.PALCE20V8H-25PC4.pdf

(27 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PALCE20V8H-25PC/4

Manufacturer:

AMD

Quantity:

7 600

Part Number:

PALCE20V8H-25PC/4

Manufacturer:

AMD

Quantity:

20 000

Dedicated Input in a Non-Registered Device

The control bit settings are SG0 = 1, SG1 = 0 and SL0

feedback signal is an adjacent I/O pin.

Combinatorial I/O in a Non-Registered Device

The control settings are SG0 = 1, SG1 = 1, and SL0

to the OR gate. The eighth product term is used to enable the output buffer. The signal at the

I/O pin is fed back to the AND array via the feedback multiplexer. This allows the pin to be used

as an input.

Combinatorial I/O in a Registered Device

The control bit settings are SG0=0,SG1=1 and SL0

to the OR gate. The eighth product term is used as the output enable. The feedback signal is the

corresponding I/O signal.

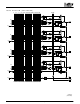

SG0

0

0

SG1

1

1

SL0 X

Device Uses Registers

0

1

Registered Output

Configuration

Combinatorial

Cell

I/O

Table 1. Macrocell Configuration

PAL20R8, 20R6,

PAL20R6, 20R4

Emulated

Devices

20R4

PALCE20V8 Family

x

SG0

x

1

1

1

= 1. Only seven product terms are available

=1. Only seven product terms are available

x

= 1. The output buffer is disabled. The

SG1

0

0

1

Device Uses No Registers

SL0 X

0

1

1

Configuration

Combinatorial

Combinatorial

Output

Input

Cell

I/O

PAL20L2, 18L4, 16L6

PAL20L2, 18L4,

Emulated

16L6, 14L8

Devices

PAL20L8

5