ISPPACCLK5610AV-01T100C LATTICE [Lattice Semiconductor], ISPPACCLK5610AV-01T100C Datasheet - Page 9

ISPPACCLK5610AV-01T100C

Manufacturer Part Number

ISPPACCLK5610AV-01T100C

Description

In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer

Manufacturer

LATTICE [Lattice Semiconductor]

Datasheet

1.ISPPACCLK5610AV-01T100C.pdf

(51 pages)

- Current page: 9 of 51

- Download datasheet (981Kb)

Lattice Semiconductor

Output Rise and Fall Times – Typical Values

Output Test Loads

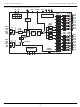

Figures 1-3-1-5 show the equivalent termination loads used to measure rise/fall times, output timing adders and

other selected parameters as noted in the various tables of this data sheet.

Figure 1-3. CMOS Termination Load

Figure 1-4. eHSTL/HSTL/SSTL Termination Load

LVTTL

LVCMOS 1.8V

LVCMOS 2.5V

LVCMOS 3.3V

SSTL18

SSTL2

SSTL3

HSTL

eHSTL

LVDS

LVPECL

1. See Figures 1-3-1-5 for test conditions.

2. Measured between 20% and 80% points.

3. Only the ‘fastest’ slew rate is available in LVDS and LVPECL modes.

Output Type

3

3

ispCLOCK

Slew 1 (Fastest)

0.54

0.75

0.57

0.55

0.55

0.50

0.50

0.60

0.55

0.25

0.20

Zo = HSTL: ~20Ω

t

R

ispClock

SSTL: 40Ω

0.76

0.69

0.69

0.77

0.40

0.40

0.45

0.45

0.40

0.20

0.20

Zo = 50Ω

t

F

50Ω/3"

0.60

0.88

0.65

0.60

—

—

—

—

—

—

—

t

R

Slew 2

50Ω/3"

50Ω/36"

0.87

0.78

0.78

0.87

—

—

—

—

—

—

—

t

F

1-9

50Ω/36"

0.78

0.83

0.99

0.78

—

—

—

—

—

—

—

t

R

1, 2

50Ω

Slew 3

ispClock5600A Family Data Sheet

1.26

1.11

0.98

1.26

950Ω

—

—

—

—

—

—

—

t

F

SCOPE

50Ω 5pF

Slew 4 (Slowest)

1.05

1.20

1.65

1.05

950Ω

VTERM

t

—

—

—

—

—

—

—

R

SCOPE

50Ω 5pF

1.88

1.68

1.51

1.88

—

—

—

—

—

—

—

t

F

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for ISPPACCLK5610AV-01T100C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

Input Hysteresis in Lattice CPLD and FPGA Devices

Manufacturer:

LATTICE [Lattice Semiconductor]

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

In-system programmable 3.3V generic digital switch

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

High performance E2CMOS PLD generic array logic, 15ns, quarter power

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: