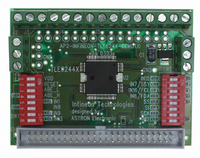

DEMOBOARD TLE 6244X Infineon Technologies, DEMOBOARD TLE 6244X Datasheet - Page 30

DEMOBOARD TLE 6244X

Manufacturer Part Number

DEMOBOARD TLE 6244X

Description

BOARD DEMO FOR TLE 6244X

Manufacturer

Infineon Technologies

Datasheet

1.TLE6244X.pdf

(70 pages)

Specifications of DEMOBOARD TLE 6244X

Main Purpose

Power Management, Low Side Driver (Internal FET)

Embedded

No

Utilized Ic / Part

TLE6244

Primary Attributes

18 Channel Internal Switch

Secondary Attributes

Overvoltage, Short-Circuit & Thermal Protection

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

DEMOBOARDTLE6244XIN

Final Data Sheet

1.7 µsec - Bus Interface

SSY

FCL

FDA

The µsec-bus-interface is one of three possibilities to control the power stages. OUT1...OUT7

and OUT9...OUT16 are influenced by the reset input RST. If RST is set to Low, these power

stages are switched off. After reset they are controlled by the SPI (default initialization of

TLE6244X). Power stage 8 however is not influenced by the reset input if it’s controlled by IN8

and U

the µsec-bus interface. Exception: OUT8 can be controlled by IN8 or by the SPI-interface only.

The bit ’Bus-Multiplex’ (BMUX) in the SPI register CONFIG prescribes parallel access (IN1...IN7,

IN9...IN16) or µsec-bus control (see figure below). Exception: If BMUX is set to ‘0’ only the power-

stages OUT1...OUT7 and OUT9...OUT16 are controlled by the µsec-bus.

Main features:

- 16 data bits for each data-frame (at the pin FDA)

- 16 clock-pulses for each data-frame (at the pin FCL)

- clock frequency TLE6244: 0...16 MHz

- one sync -input (pin SSY) to latch the input data stream

- input level interface same as for IN6, IN7, IN16

- no error correction

Principle of the µsec-bus interface

FDA

FCL

SSY

SPI

VDD

> 3,5V. Alternatively these outputs can be controlled either by the pins IN1...IN16 or by

Filter

Glitch

D0

16 bit shift register

16 bit µsec-bus Reg.

SCON_REG

SPI-shift-reg

D1

30

Data-Frame

INx

D14

BMUX

MUX_REG

D15

don’t care

TLE 6244X

V4.2, 2003-08-29

OUTx

D0