C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 208

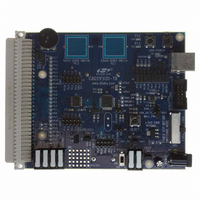

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 208 of 324

- Download datasheet (3Mb)

C8051F93x-C8051F92x

Internal Register Definition 20.4. RTC0CN: SmaRTClock Control

SmaRTClock Address = 0x04

208

Note: The ALRM flag will remain asserted for a maximum of one SmaRTClock cycle. See Section “Power

Reset

Name

Type

Bit

7

6

5

4

3

2

1

0

Bit

RTC0AEN SmaRTClock Alarm Enable.

RTC0CAP SmaRTClock Timer Capture.

RTC0SET SmaRTClock Timer Set.

Management” on page 156 for information on how to capture a SmaRTClock Alarm event using a flag which

is not automatically cleared by hardware.

MCLKEN Missing SmaRTClock Detector Enable.

OSCFAIL SmaRTClock Oscillator Fail Event Flag.

RTC0EN SmaRTClock Enable.

RTC0TR SmaRTClock Timer Run Control.

Name

ALRM

RTC0EN

R/W

7

0

Enables/disables the SmaRTClock oscillator and associated bias currents.

0: SmaRTClock oscillator disabled.

1: SmaRTClock oscillator enabled.

Enables/disables the missing SmaRTClock detector.

0: Missing SmaRTClock detector disabled.

1: Missing SmaRTClock detector enabled.

Set by hardware when a missing SmaRTClock detector timeout occurs. Must be

cleared by software. The value of this bit is not defined when the SmaRTClock

oscillator is disabled.

Controls if the SmaRTClock timer is running or stopped (holds current value).

0: SmaRTClock timer is stopped.

1: SmaRTClock timer is running.

Enables/disables the SmaRTClock alarm function. Also clears the ALRM flag.

0: SmaRTClock alarm disabled.

1: SmaRTClock alarm enabled.

SmaRTClock Alarm Event

Flag and Auto Reset

Enable

Reads return the state of the

alarm event flag.

Writes enable/disable the

Auto Reset function.

Writing 1 initiates a SmaRTClock timer set operation. This bit is cleared to 0 by hard-

ware to indicate that the timer set operation is complete.

Writing 1 initiates a SmaRTClock timer capture operation. This bit is cleared to 0 by

hardware to indicate that the timer capture operation is complete.

MCLKEN

R/W

0

6

OSCFAIL

Varies

R/W

5

RTC0TR

R/W

Rev. 1.1

Read:

0: SmaRTClock alarm

event flag is de-asserted.

1: SmaRTClock alarm

event flag is asserted.

4

0

Function

RTC0AEN

R/W

3

0

ALRM

R/W

2

0

Write:

0: Disable Auto Reset.

1: Enable Auto Reset.

RTC0SET RTC0CAP

R/W

1

0

R/W

0

0

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc