C8051F313-GM Silicon Laboratories Inc, C8051F313-GM Datasheet - Page 27

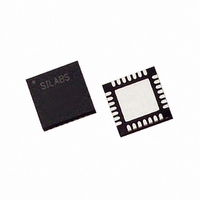

C8051F313-GM

Manufacturer Part Number

C8051F313-GM

Description

IC 8051 MCU 8K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F31xr

Specifications of C8051F313-GM

Core Size

8-Bit

Program Memory Size

8KB (8K x 8)

Oscillator Type

Internal

Core Processor

8051

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Program Memory Type

FLASH

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 17x10b

Operating Temperature

-40°C ~ 85°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

No. Of I/o's

25

Ram Memory Size

1280Byte

Cpu Speed

25MHz

No. Of Timers

4

No. Of Pwm Channels

5

Digital Ic Case

RoHS Compliant

Rohs Compliant

Yes

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

I2C, SMBus, SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

25

Number Of Timers

5

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F310DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit

Data Rom Size

128 B

Height

0.88 mm

Length

5 mm

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.7 V

Width

5 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

770-1006 - ISP 4PORT FOR SILABS C8051F MCU

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

336-1256

- Current page: 27 of 228

- Download datasheet (2Mb)

1.1.

1.1.1. Fully 8051 Compatible

The C8051F31x family utilizes Silicon Laboratories' proprietary CIP-51 microcontroller core. The CIP-51 is

fully compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be

used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052, includ-

ing four 16-bit counter/timers, a full-duplex UART with extended baud rate configuration, an enhanced SPI

port, 1280 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 29/25/21

I/O pins.

1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the stan-

dard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system

clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core exe-

cutes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than

four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that

require each execution time.

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.9

shows a comparison of peak throughputs for various 8-bit microcontroller cores with their maximum sys-

tem clocks.

Number of Instructions

Clocks to Execute

CIP-51™ Microcontroller Core

Figure 1.9. Comparison of Peak MCU Execution Speeds

25

20

15

10

5

26

1

(25 MHz clk)

Silicon Labs

CIP-51

50

2

2/3

(33 MHz clk)

PIC17C75x

Rev. 1.7

5

Microchip

C8051F310/1/2/3/4/5/6/7

14

3

(33 MHz clk)

Philips

80C51

3/4

7

(16 MHz clk)

4

3

ADuC812

8051

4/5

1

5

2

8

1

27

Related parts for C8051F313-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc