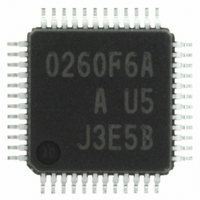

M30260F6AGP#U5A Renesas Electronics America, M30260F6AGP#U5A Datasheet - Page 102

M30260F6AGP#U5A

Manufacturer Part Number

M30260F6AGP#U5A

Description

IC M16C MCU FLASH 48K 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Datasheet

1.M30260F3AGPU5A.pdf

(354 pages)

Specifications of M30260F6AGP#U5A

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

48-LQFP

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

UART

Total Internal Ram Size

2KB

# I/os (max)

39

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-20C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Package

48LQFP

Family Name

R8C

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16 Bit

Number Of Programmable I/os

39

Number Of Timers

8

For Use With

R0K33026AS000BE - KIT DEV EVALUATION M16C/26A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30260F6AGP#U5AM30260F6AGP#D3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 102 of 354

- Download datasheet (4Mb)

R

R

M

e

E

. v

J

1

Table 11.1 DMAC Specifications

0

No. of channels

Transfer memory space

Maximum No. of bytes transferred

DMA request factors

Channel priority

Transfer unit

Transfer address direction

Transfer mode Single transfer

DMA interrupt request generation timing When the DMAi transfer counter underflowed

DMA startup

DMA shutdown Single transfer

N OTES:

6

2. The selectable causes of DMA requests differ with each channel.

3. Make sure that no DMAC-related registers (addresses 0020

1. DMA transfer is not effective to any interrupt. DMA transfer is affected neither by the I flag nor by the

2

9

C

0 .

B

2 /

interrupt control register.

0

0

2

6

0

F

A

2

e

0 -

b

G

1 .

2

o r

0

, 5

0

u

Item

2

p

0

(

Repeat transfer When the DMAE bit is set to “0” (disabled)

0

Repeat transfer When the DMAi transfer counter underflows, it is reloaded with the value

M

7

1

6

page 83

C

(1, 2)

2 /

6

, A

M

f o

1

6

3

C

2

2 (cycle steal method)

• From any address in the 1M bytes space to a fixed address

• From a fixed address to any address in the 1M bytes space

• From a fixed address to a fixed address

128K bytes (with 16-bit transfers) or 64K bytes (with 8-bit transfers)

Falling edge of INT0 or INT1

Both edge of INT0 or INT1

Timer A0 to timer A4 interrupt requests

Timer B0 to timer B2 interrupt requests

UART0 transfer, UART0 reception interrupt requests

UART1 transfer, UART1 reception interrupt requests

UART2 transfer, UART2 reception interrupt requests

A/D conversion interrupt requests

Software triggers

DMA0 > DMA1 (DMA0 takes precedence)

8 bits or 16 bits

forward or fixed (The source and destination addresses cannot both be

in the forward direction.)

Transfer is completed when the DMAi transfer counter (i = 0,1)

underflows after reaching the terminal count.

of the DMAi transfer counter reload register and a DMA transfer is con

tinued with it.

Data transfer is initiated each time a DMA request is generated when the

DMAE bit in the DMAiCON register is set to “1” (enabled).

• When the DMAE bit is set to “0” (disabled)

• After the DMAi transfer counter underflows

When a data transfer is started after setting the DMAE bit to “1” (en

abled), the forward address pointer is reloaded with the value of the

SARi or the DARi pointer whichever is specified to be in the forward

direction and the DMAi transfer counter is reloaded with the value of the

DMAi transfer counter reload register.

9

2 /

6

, B

M

1

6

C

2 /

________

6

________

) T

________

________

Specification

16

to 003F

16

) are accessed by the DMAC.

11. DMAC

Related parts for M30260F6AGP#U5A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: