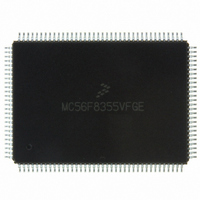

MC56F8355VFGE Freescale Semiconductor, MC56F8355VFGE Datasheet - Page 122

MC56F8355VFGE

Manufacturer Part Number

MC56F8355VFGE

Description

IC DSP 16BIT 60MHZ 128-LQFP

Manufacturer

Freescale Semiconductor

Series

56F8xxxr

Datasheet

1.MC56F8355VFGE.pdf

(172 pages)

Specifications of MC56F8355VFGE

Core Processor

56800

Core Size

16-Bit

Speed

60MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

49

Program Memory Size

264KB (132K x 16)

Program Memory Type

FLASH

Ram Size

10K x 16

Voltage - Supply (vcc/vdd)

2.25 V ~ 3.6 V

Data Converters

A/D 16x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 105°C

Package / Case

128-LQFP

Data Bus Width

16 bit

Processor Series

MC56F83xx

Core

56800E

Numeric And Arithmetic Format

Fixed-Point

Device Million Instructions Per Second

60 MIPs

Maximum Clock Frequency

60 MHz

Number Of Programmable I/os

49

Data Ram Size

20 KB

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Interface Type

SCI, SPI, CAN

Minimum Operating Temperature

- 40 C

For Use With

MC56F8367EVME - EVAL BOARD FOR MC56F83X

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC56F8355VFGE

Manufacturer:

Freescale

Quantity:

562

Company:

Part Number:

MC56F8355VFGE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC56F8355VFGE

Manufacturer:

FREESCALE

Quantity:

20 000

The 56800E core contains both STOP and WAIT instructions. Both put the CPU to sleep. For lowest

power consumption in Stop mode, the PLL can be shut down. This must be done explicitly before entering

Stop mode, since there is no automatic mechanism for this. When the PLL is shut down, the 56800E

system clock must be set equal to the oscillator output.

Some applications require the 56800E STOP and WAIT instructions to be disabled. To disable those

instructions, write to the SIM control register (SIM_CONTROL), described in

can be on either a permanent or temporary basis. Permanently assigned applications last only until their

next reset.

6.9 Resets

The SIM supports four sources of reset. The two asynchronous sources are the external RESET pin and

the Power-On Reset (POR). The two synchronous sources are the software reset, which is generated within

the SIM itself by writing to the SIM_CONTROL register, and the COP reset.

Reset begins with the assertion of any of the reset sources. Release of reset to various blocks is sequenced

to permit proper operation of the device. A POR reset is first extended for 2

stabilization of the clock source, followed by a 32 clock window in which SIM clocking is initiated. It is

then followed by a 32 clock window in which peripherals are released to implement Flash security, and,

finally, followed by a 32 clock window in which the core is initialized. After completion of the described

reset sequence, application code will begin execution.

Resets may be asserted asynchronously, but are always released internally on a rising edge of the system

clock.

Part 7 Security Features

The 56F8355/56F8155 offer security features intended to prevent unauthorized users from reading the

contents of the Flash Memory (FM) array. The Flash security consists of several hardware interlocks that

block the means by which an unauthorized user could gain access to the Flash array.

However, part of the security must lie with the user’s code. An extreme example would be user’s code that

dumps the contents of the internal program, as this code would defeat the purpose of security. At the same

time, the user may also wish to put a “backdoor” in his program. As an example, the user downloads a

security key through the SCI, allowing access to a programming routine that updates parameters stored in

another section of the Flash.

7.1 Operation with Security Enabled

Once the user has programmed the Flash with his application code, the device can be secured by

programming the security bytes located in the FM configuration field, which occupies a portion of the FM

array. These non-volatile bytes will keep the part secured through reset and through power-down of the

device. Only two bytes within this field are used to enable or disable security. Refer to the Flash Memory

section in the 56F8300 Peripheral User Manual for the state of the security bytes and the resulting state

122

56F8355 Technical Data, Rev. 17

Part

21

clock cycles to permit

6.5.1. This procedure

Freescale Semiconductor

Preliminary