AT89S8252-24PI Atmel, AT89S8252-24PI Datasheet - Page 10

AT89S8252-24PI

Manufacturer Part Number

AT89S8252-24PI

Description

MCU W/SPI 8KB FLSH 2K EEP 40-DIP

Manufacturer

Atmel

Series

89Sr

Datasheet

1.AT89S8252-24AC.pdf

(41 pages)

Specifications of AT89S8252-24PI

Core Processor

8051

Core Size

8-Bit

Speed

24MHz

Connectivity

SPI, UART/USART

Peripherals

POR, WDT

Number Of I /o

32

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 6 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

40-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Data Converters

-

Other names

AT89S825224PI

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATM

Quantity:

4 000

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATM

Quantity:

3 500

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATMEL

Quantity:

2 360

Part Number:

AT89S8252-24PI

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

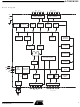

Table 5. SPSR – SPI Status Register

Table 6. SPDR – SPI Data Register

Data Memory –

EEPROM and RAM

10

SPSR Address = AAH

Symbol

SPIF

WCOL

SPDR Address = 86H

Bit

Bit

AT89S8252

SPIF

SPD7

Function

SPI Interrupt Flag. When a serial transfer is complete, the SPIF bit is set and an interrupt is generated if SPIE = 1 and ES

= 1. The SPIF bit is cleared by reading the SPI status register with SPIF and WCOL bits set, and then reading/writing the

SPI data register.

Write Collision Flag. The WCOL bit is set if the SPI data register is written during a data transfer. During data transfer, the

result of reading the SPDR register may be incorrect, and writing to it has no effect. The WCOL bit (and the SPIF bit) are

cleared by reading the SPI status register with SPIF and WCOL set, and then accessing the SPI data register.

7

7

WCOL

SPD6

6

6

The AT89S8252 implements 2K bytes of on-chip EEPROM for data storage and 256

bytes of RAM. The upper 128 bytes of RAM occupy a parallel space to the Special

Function Registers. That means the upper 128 bytes have the same addresses as the

SFR space but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the address

mode used in the instruction specifies whether the CPU accesses the upper 128 bytes

of RAM or the SFR space. Instructions that use direct addressing access SFR space.

For example, the following direct addressing instruction accesses the SFR at location

0A0H (which is P2).

Instructions that use indirect addressing access the upper 128 bytes of RAM. For exam-

ple, the following indirect addressing instruction, where R0 contains 0A0H, accesses the

data byte at address 0A0H, rather than P2 (whose address is 0A0H).

Note that stack operations are examples of indirect addressing, so the upper 128 bytes

of data RAM are available as stack space.

The on-chip EEPROM data memory is selected by setting the EEMEN bit in the

WMCON register at SFR address location 96H. The EEPROM address range is from

000H to 7FFH. The MOVX instructions are used to access the EEPROM. To access off-

chip data memory with the MOVX instructions, the EEMEN bit needs to be set to “0”.

The EEMWE bit in the WMCON register needs to be set to “1” before any byte location

in the EEPROM can be written. User software should reset EEMWE bit to “0” if no fur-

ther EEPROM write is required. EEPROM write cycles in the serial programming mode

are self-timed and typically take 2.5 ms. The progress of EEPROM write can be moni-

tored by reading the RDY/BSY bit (read-only) in SFR WMCON. RDY/BSY = 0 means

SPD5

MOV 0A0H, #data

MOV @R0, #data

–

5

5

SPD4

–

4

4

SPD3

3

–

3

SPD2

2

–

2

Reset Value = 00XX XXXXB

Reset Value = unchanged

SPD1

1

–

1

SPD0

0

–

0

0401G–MICRO–3/06