AT89S8252-24PI Atmel, AT89S8252-24PI Datasheet - Page 2

AT89S8252-24PI

Manufacturer Part Number

AT89S8252-24PI

Description

MCU W/SPI 8KB FLSH 2K EEP 40-DIP

Manufacturer

Atmel

Series

89Sr

Datasheet

1.AT89S8252-24AC.pdf

(41 pages)

Specifications of AT89S8252-24PI

Core Processor

8051

Core Size

8-Bit

Speed

24MHz

Connectivity

SPI, UART/USART

Peripherals

POR, WDT

Number Of I /o

32

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 6 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

40-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Data Converters

-

Other names

AT89S825224PI

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATM

Quantity:

4 000

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATM

Quantity:

3 500

Company:

Part Number:

AT89S8252-24PI

Manufacturer:

ATMEL

Quantity:

2 360

Part Number:

AT89S8252-24PI

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

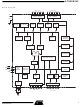

Pin Configurations

Pin Description

VCC

GND

Port 0

Port 1

2

AT89S8252

(T2 EX) P1.1

(MOSI) P1.5

(MISO) P1.6

(INT0) P3.2

(INT1) P3.3

(SCK) P1.7

(RXD) P3.0

(TXD) P3.1

(WR) P3.6

(RD) P3.7

(SS) P1.4

(T2) P1.0

(T0) P3.4

(T1) P3.5

XTAL2

XTAL1

GND

P1.2

P1.3

RST

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

PDIP

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VCC

P0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA/VPP

ALE/PROG

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

P2.4 (A12)

P2.3 (A11)

P2.2 (A10)

P2.1 (A9)

P2.0 (A8)

Supply voltage.

Ground.

Port 0 is an 8-bit open drain bi-didirectional I/O port. As an output port, each pin can

sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-

impedance inputs.

Port 0 can also be configured to be the multiplexed low-order address/data bus during

accesses to external program and data memory. In this mode, P0 has internal pull-ups.

Port 0 also receives the code bytes during Flash programming and outputs the code

bytes during program verification. External pull-ups are required during program

verification.

Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 1 output buffers

can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high

by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are exter-

nally being pulled low will source current (I

(MOSI) P1.5

(MISO) P1.6

(RXD) P3.0

(INT0) P3.2

(INT1) P3.3

(SCK) P1.7

(TXD) P3.1

(T0) P3.4

(T1) P3.5

RST

NC

7

8

9

10

11

12

13

14

15

16

17

PLCC

39

38

37

36

35

34

33

32

31

30

29

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA/VPP

NC

ALE/PROG

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

(MOSI) P1.5

(MISO) P1.6

(RXD) P3.0

(INT0) P3.2

(INT1) P3.3

(SCK) P1.7

(TXD) P3.1

(T0) P3.4

(T1) P3.5

RST

IL

NC

) because of the internal pull-ups.

1

2

3

4

5

6

7

8

9

10

11

TQFP

33

32

31

30

29

28

27

26

25

24

23

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA/VPP

NC

ALE/PROG

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

0401G–MICRO–3/06