XR88C681CP/40 Exar Corporation, XR88C681CP/40 Datasheet - Page 37

XR88C681CP/40

Manufacturer Part Number

XR88C681CP/40

Description

Dual Channel UART

Manufacturer

Exar Corporation

Datasheet

1.XR88C681CP40-F.pdf

(101 pages)

Specifications of XR88C681CP/40

Features

*

Number Of Channels

2, DUART

Fifo's

1 Byte, 3 Byte

Voltage - Supply

5V

With Parallel Port

Yes

With Cmos

Yes

Mounting Type

Through Hole

Package / Case

40-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR88C681CP/40

Manufacturer:

TP

Quantity:

6 238

Part Number:

XR88C681CP/40

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

Company:

Part Number:

XR88C681CP/40-F

Manufacturer:

Linear

Quantity:

185

Accumulator.

capture functions; and four of the output pins support

output compare functions.

Port B

Port B consists of 8 output pins. If the 68HC11 C is

operating in the single chip mode, this port functions as a

general purpose output port. However, if the 68HC11 is

operating in the expanded-multiplexed mode, then this

port will function as the upper address byte for

memory/peripheral device interfacing (A8 - A15).

Port C

Port C consists of 8 bi-directional pins. When the 68HC11

is operating in the single-chip mode, this port functions as

a general purpose bi-directional port. However, if the

68HC11 is operating in the expanded-multiplexed mode

then this port will function as the multiplexed address/data

bus (AD0 - AD7). Specifically, during the first half of a

memory cycle, this port will function as the lower address

byte (Port B is the upper address byte) for addressing

memory devices and peripheral components. During the

second half of the memory cycle, this port will function as

the bi-directional data bus.

demultiplexed via the use of the AS (Address Strobe) pin

and a 74LS373 latch device.

Port D

Port D consists of 8 bi-directional pins. However, this port

can be configured to support the on-chip Serial Peripheral

Interface (SPI), and Serial Communications Interface

(SCI).

Port E

Port E consists of either 4 or 8 inputs (depending upon the

packaging option). This port can be configured to function

as a general purpose input or as the inputs to the on-chip

A/D converter.

There are numerous other pins that are pertinent for

interfacing to the XR88C681 DUART device. Some of

these pins are discussed here.

Rev. 2.11

Three of the input pins support input

This port can be

37

IRQ

This is the “maskable” interrupt request input. If this input

is asserted (e.g., toggled “low”), then the 68HC11 C will

branch program control to FFF2, FFF3 in system memory

(on-chip ROM). The user is responsible for insuring that

the appropriate interrupt service routine resides at this

location in memory.

AS/STRA

AS or “Address Strobe” can be used to demultiplex the

address/data bus of Port C. This pin is at a logic “high”

during the first half of a memory cycle; and at a logic “low”

during the second half of a memory cycle.

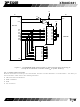

If the 68HC11 is intended to operate in the

expanded-multiplexed mode and interface to more than

256 bytes of addressable memory space, then both Ports

B and C are required as shown in Figure 13. Figure 13

also illustrates how the XR88C681 DUART could be

connected to the 68HC11

operation. If the DUART requests an interrupt, its active

low

turn, cause the

this occurs the C will continue executing its current

instruction. After completion of this instruction, program

control will shift to location FFF2, FFF3 in system

memory.

DUART’s interrupt service routine resides at this location

in memory.

acknowledge signal to the DUART. Instead, the C will

just processes through the interrupt service routine.

Once the C has eliminated the cause(s) of the DUART’s

interrupt request, the

will return from the Interrupt Service Routine and resume

normal processing.

One more point should be mentioned about Figure 13.

The glue-logic circuitry required to generate the -WR,

-RD, and the RESET signals for the DUART, from the

-R/W, -RESET, and E clock presented in Figure 2. This

circuitry has also been included in Figure 14.

-

INTR pin will be asserted (toggle low), which will, in

The user is responsible to insure that the

-

IRQ pin of the CPU to be asserted. When

The

-

INTR pin will be negated and the C

C will not issue an interrupt

XR88C681

C for interrupt driven