MPC8309VMAHFCA Freescale Semiconductor, MPC8309VMAHFCA Datasheet - Page 4

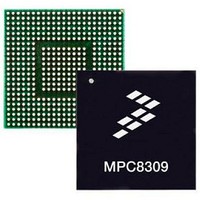

MPC8309VMAHFCA

Manufacturer Part Number

MPC8309VMAHFCA

Description

417/333/233 MP Std Tmp

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC8309VMAHFCA.pdf

(81 pages)

Specifications of MPC8309VMAHFCA

Processor Series

MPC8309

Core

e300c3

Data Bus Width

32 bit

Data Ram Size

512 MB

Interface Type

USB, CAN, UART, PCI

Maximum Clock Frequency

417 MHz

Number Of Programmable I/os

56

Operating Supply Voltage

- 0.3 V to + 1.26 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Operating Temperature Range

0 C to + 105 C

Processor To Be Evaluated

MPC8309

Supply Current (max)

5 uA

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8309VMAHFCA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Overview

4

•

•

•

MPC8309 PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

For more information on QUICC Engine sub-modules, see QUICC Engine Block Reference

Manual with Protocol Interworking.

DDR SDRAM memory controller

— Programmable timing supporting DDR2 SDRAM

— Integrated SDRAM clock generation

— Supports 8-bit ECC

— 16/32-bit data interface, up to 333-MHz data rate

— 14 address lines

— The following SDRAM configurations are supported:

— One 16-bit device or two 8-bit devices on a 16-bit bus, or two 16-bit devices or four 8-bit

— Two clock pair to support up to 4 DRAM devices

— Supports auto refresh

— On-the-fly power management using CKE

Enhanced local bus controller (eLBC)

— Multiplexed 26-bit address and 8-/16-bit data operating at up to 66 MHz

— Eight chip selects supporting eight external slaves

— Supports boot from parallel NOR Flash and parallel NAND Flash

— Supports programmable clock ratio dividers

— Up to eight-beat burst transfers

— 16- and 8-bit ports, separate LWE for each 8 bit

— Three protocol engines available on a per chip select basis:

— Variable memory block sizes for FCM, GPCM, and UPM mode

— Default boot ROM chip select with configurable bus width (8 or 16)

— Provides two Write Enable signals to allow single byte write access to external 16-bit eLBC

Integrated programmable interrupt controller (IPIC)

— Functional and programming compatibility with the MPC8260 interrupt controller

— Support for external and internal discrete interrupt sources

— Programmable highest priority request

– Up to two physical banks (chip selects), 512-Mbyte addressable space for 32 bit data

– 64-Mbit to 2-Gbit devices with x8/x16/x32 data ports (no direct x4 support)

devices on a 32-bit bus Support for up to 16 simultaneous open pages for DDR2

– Four chip selects dedicated

– Four chip selects offered as multiplexed option

– General-purpose chip select machine (GPCM)

– Three user programmable machines (UPMs)

– NAND Flash control machine (FCM)

slave devices

interface

Freescale Semiconductor