EP1S40F1020C6 Altera, EP1S40F1020C6 Datasheet - Page 95

EP1S40F1020C6

Manufacturer Part Number

EP1S40F1020C6

Description

IC STRATIX FPGA 40K LE 1020-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S40F1020C6

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

773

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1020-FBGA

Family Name

Stratix

Number Of Logic Blocks/elements

41250

# I/os (max)

773

Frequency (max)

450.05MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

41250

Ram Bits

3423744

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

1020

Package Type

FC-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-1425

EP1S40SF1020C6

EP1S40SF1020C6

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S40F1020C6

Manufacturer:

ALTERA

Quantity:

784

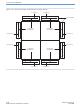

Figure 2–48. EP1S30, EP1S40, EP1S60, EP1S80 Device I/O Clock Groups

Altera Corporation

July 2005

IO_CLKM[7:0]

IO_CLKO[7:0]

IO_CLKN[7:0]

IO_CLKP[7:0]

8

8

8

8

IO_CLKA[7:0]

22 Clocks in the

22 Clocks in the

Half-Quadrant

Half-Quadrant

8

IO_CLKL[7:0]

You can use the Quartus II software to control whether a clock input pin

is either global, regional, or fast regional. The Quartus II software

automatically selects the clocking resources if not specified.

Enhanced & Fast PLLs

Stratix devices provide robust clock management and synthesis using up

to four enhanced PLLs and eight fast PLLs. These PLLs increase

performance and provide advanced clock interfacing and clock-

frequency synthesis. With features such as clock switchover, spread

spectrum clocking, programmable bandwidth, phase and delay control,

and PLL reconfiguration, the Stratix device’s enhanced PLLs provide you

with complete control of your clocks and system timing. The fast PLLs

8

IO_CLKB[7:0]

22 Clocks in the

22 Clocks in the

Half-Quadrant

Half-Quadrant

8

IO_CLKK[7:0]

8

IO_CLKC[7:0]

22 Clocks in the

22 Clocks in the

Half-Quadrant

Half-Quadrant

8

IO_CLKJ[7:0]

8

IO_CLKD[7:0]

22 Clocks in the

22 Clocks in the

Half-Quadrant

Half-Quadrant

Stratix Device Handbook, Volume 1

8

IO_CLKI[7:0]

8

Stratix Architecture

8

8

8

8

IO_CLKE[7:0]

IO_CLKF[7:0]

IO_CLKG[7:0]

IO_CLKH[7:0]

I/O Clock Regions

2–81