EP2SGX90FF1508C3N Altera, EP2SGX90FF1508C3N Datasheet - Page 304

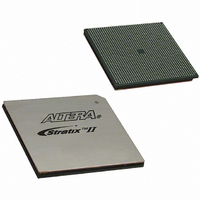

EP2SGX90FF1508C3N

Manufacturer Part Number

EP2SGX90FF1508C3N

Description

IC STRATIX II GX 90K 1508-FBGA

Manufacturer

Altera

Series

Stratix® II GXr

Datasheet

1.EP2SGX90FF1508C3N.pdf

(314 pages)

Specifications of EP2SGX90FF1508C3N

Number Of Logic Elements/cells

90960

Number Of Labs/clbs

4548

Total Ram Bits

4520448

Number Of I /o

650

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 70°C

Package / Case

1508-FBGA

For Use With

544-1725 - PCIE KIT W/S II GX EP2SGX90N544-1724 - SI KIT W/SII GX EP2SGX90N544-1702 - VIDEO KIT W/SII GX EP2SGX90N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1772

EP2SGX90FF40C3N

EP2SGX90FF40C3NES

EP2SGX90FF40C3N

EP2SGX90FF40C3NES

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2SGX90FF1508C3N

Manufacturer:

ALTERA30

Quantity:

121

- Current page: 304 of 314

- Download datasheet (4Mb)

JTAG Timing Specifications

JTAG Timing

Specifications

Figure 4–14. Stratix II GX JTAG Waveforms.

4–134

Stratix II GX Device Handbook, Volume 1

Captured

Driven

Signal

Signal

to be

to be

TMS

TDO

TCK

TDI

t

JCH

Figure 4–14

t

Notes to

(1)

(2)

(3)

t

JPZX

JSZX

Table 4–116. DQS Phase Offset Delay Per Stage (ps)

t

JCP

The delay settings are linear.

The valid settings for phase offset are -32 to +31.

The typical value equals the average of the minimum and maximum values.

t

Speed Grade

JSSU

t

JCL

Table

-3

-4

-5

shows the timing requirements for the JTAG signals

4–116:

t

JSH

t

t

JPCO

JSCO

t

JPSU

Min

10

10

10

Positive Offset

t

t

JSXZ

JPH

Max

15

15

16

t

JPXZ

Min

Negative Offset

Notes

8

8

8

Altera Corporation

(1), (2),

October 2007

Max

11

11

12

(3)

Related parts for EP2SGX90FF1508C3N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: