TP3064J National Semiconductor, TP3064J Datasheet - Page 3

TP3064J

Manufacturer Part Number

TP3064J

Description

IC FILTER MONO SRL COMBO 20DIP

Manufacturer

National Semiconductor

Type

PCM Codec/Filterr

Datasheet

1.TP3067VNOPB.pdf

(18 pages)

Specifications of TP3064J

Data Interface

Serial

Resolution (bits)

8 b

Number Of Adcs / Dacs

1 / 1

Sigma Delta

No

Voltage - Supply, Analog

4.75 V ~ 5.25 V

Voltage - Supply, Digital

4.75 V ~ 5.25 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Through Hole

Package / Case

20-CDIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

*TP3064J

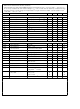

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

TP3064J

Manufacturer:

NS/国半

Quantity:

20 000

Functional Description

POWER-UP

When power is first applied power-on reset circuitry initializ-

es the COMBO

non-essential circuits are deactivated and the D

VPO

To power-up the device a logical low level or clock must be

applied to the MCLK

must be present Thus 2 power-down control modes are

available The first is to pull the MCLK

alternative is to hold both FS

low the device will power-down approximately 2 ms after

the last FS

FS

will remain in the high impedance state until the second FS

pulse

SYNCHRONOUS OPERATION

For synchronous operation the same master clock and bit

clock should be used for both the transmit and receive di-

rections In this mode a clock must be applied to MCLK

and the MCLK

control A low level on MCLK

and a high level powers down the device In either case

MCLK

transmit and receive circuits A bit clock must also be ap-

plied to BCLK

select the proper internal divider for a master clock of 1 536

MHz 1 544 MHz or 2 048 MHz For 1 544 MHz operation

the device automatically compensates for the 193rd clock

pulse each frame

With a fixed level on the BCLK

selected as the bit clock for both the transmit and receive

directions Table I indicates the frequencies of operation

which can be selected depending on the state of BCLK

CLKSEL In this synchronous mode the bit clock BCLK

may be from 64 kHz to 2 048 MHz but must be synchro-

nous with MCLK

Each FS

data from the previous encode cycle is shifted out of the

enabled D

bit clock periods the TRI-STATE D

high impedance state With an FS

latched via the D

BCLK

MCLK

ASYNCHRONOUS OPERATION

For asynchronous operation separate transmit and receive

clocks may be applied MCLK

MHz for the TP3067 or 1 536 MHZ 1 544 MHz for the

TP3064 and need not be synchronous For best transmis-

BCLK

Clocked

0

1

X

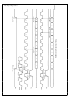

TABLE I Selection of Master Clock Frequencies

b

or FS

R

X

X R

and VPO

if running) FS

will be selected as the master clock for both the

R

X

X

R

X

pulse begins the encoding cycle and the PCM

CLKSEL

output on the positive edge of BCLK

pulse The TRI-STATE PCM data output D

or FS

X

R

TM

a

X

and the BCLK

R

PDN pin can be used as a power-down

and places it into a power-down state All

outputs are put in high impedance states

R

input on the negative edge of BCLK

R

pulse Power-up will occur on the first

X

PDN pin and FS

and FS

1 536 MHz or

2 048 MHz

1 544 MHz

2 048 MHz

TP3067

X

R

R

X

Frequency Selected

and FS

R

R

PDN powers up the device

and MCLK

CLKSEL pin BLCK

must be synchronous with

CLKSEL can be used to

Master Clock

X

R

output is returned to a

R

X

R

pulse PCM data is

inputs continuously

and or FS

PDN pin high the

R

1 536 MHz or

1 536 MHz or

1 544 MHz

2 048 MHz

1 544 MHz

must be 2 048

TP3064

X

X

R

X

After 8

VF

pulses

will be

X

R

(or

R

O

X

X

X

X

3

Figure 3 Based on the transmit frame sync FS

sion performance however MCLK

with MCLK

logic levels to the MCLK

connect MCLK

Description) For 1 544 MHz operation the device automati-

cally compensates for the 193rd clock pulse each frame

FS

with MCLK

and must be synchronous with BCLK

clock the logic levels shown in Table I are not valid in asyn-

chronous mode BCLK

kHz to 2 048 MHz

SHORT FRAME SYNC OPERATION

The COMBO can utilize either a short frame sync pulse (the

same as the TP3020 21 CODECs) or a long frame sync

pulse Upon power initialization the device assumes a short

frame mode In this mode both frame sync pulses FS

FS

ships specified in Figure 2 With FS

edge of BCLK

D

The following seven rising edges clock out the remaining

seven bits and the next falling edge disables the D

With FS

synchronous mode) the next falling edge of BCLK

in the sign bit The following seven falling edges latch in the

seven remaining bits All devices may utilize the short frame

sync pulse in synchronous or asynchronous operating

mode

LONG FRAME SYNC OPERATION

To use the long (TP5116A 56 CODECs) frame mode both

the frame sync pulses FS

bit clock periods long with timing relationships specified in

BO will sense whether short or long frame sync pulses are

being used For 64 kHz operation the frame sync pulse

must be kept low for a minimum of 160 ns The D

STATE output buffer is enabled with the rising edge of FS

or the rising edge of BCLK

first bit clocked out is the sign bit The following seven

BCLK

D

the eighth rising edge or by FS

comes later A rising edge on the receive frame sync pulse

FS

next eight falling edges of BCLK

mode) All devices may utilize the long frame sync pulse in

synchronous or asynchronous mode

TRANSMIT SECTION

The transmit section input is an operational amplifier with

provision for gain adjustment using two external resistors

see Figure 4 The low noise and wide bandwidth allow gains

in excess of 20 dB across the audio passband to be real-

ized The op amp drives a unity-gain filter consisting of RC

active pre-filter followed by an eighth order switched-ca-

pacitor bandpass filter clocked at 256 kHz The output of

this filter directly drives the encoder sample-and-hold circuit

The A D is of companding type according to

(TP3064) or A-law (TP3067) coding conventions A preci-

sion voltage reference is trimmed in manufacturing to pro-

vide an input overload (t

X

X

X

R

R

TRI-STATE output buffer which will output the sign bit

output is disabled by the falling BCLK

starts each encoding cycle and must be synchronous

must be one bit clock period long with timing relation-

will cause the PCM data at D

X

rising edges clock out the remaining seven bits The

R

X

high during a falling edge of BCLK

X

which is easily achieved by applying only static

and BCLK

X

X

the next rising edge of BCLK

to all internal MCLK

X

X

MAX

R

and BCLK

X

X

FS

PDN pin This will automatically

and FS

whichever comes later and the

) of nominally 2 5V peak (see

R

starts each decoding cycle

R

R

R

R

X

(BCLK

R

should be synchronous

to be latched in on the

X

must be three or more

going low whichever

may operate from 64

R

R

high during a falling

functions (see Pin

BCLK

X

X

in synchronous

edge following

X

R

R

X

enables the

must be a

(BCLK

the COM-

R

X

latches

output

X

X

TRI-

-law

X

and

in

X