TP3064J National Semiconductor, TP3064J Datasheet - Page 7

TP3064J

Manufacturer Part Number

TP3064J

Description

IC FILTER MONO SRL COMBO 20DIP

Manufacturer

National Semiconductor

Type

PCM Codec/Filterr

Datasheet

1.TP3067VNOPB.pdf

(18 pages)

Specifications of TP3064J

Data Interface

Serial

Resolution (bits)

8 b

Number Of Adcs / Dacs

1 / 1

Sigma Delta

No

Voltage - Supply, Analog

4.75 V ~ 5.25 V

Voltage - Supply, Digital

4.75 V ~ 5.25 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Through Hole

Package / Case

20-CDIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

*TP3064J

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

TP3064J

Manufacturer:

NS/国半

Quantity:

20 000

Symbol

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

RM

FM

PB

RB

FB

WMH

WML

SBFM

SFFM

WBH

WBL

HBFL

HBFS

SFB

DBD

DBTS

DZC

DZF

SDB

HBD

SF

HF

HBFI

WFL

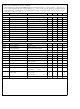

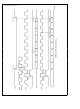

Timing Specifications

Unless otherwise noted limits printed in BOLD characters are guaranteed for V

0 C to 70 C by correlation with 100% electrical testing at T

production tests and or product design and characterization All signals are referenced to GNDA Typicals specified at V

a

See Definitions and Timing Conventions section for test methods information

1 t

5 0V V

PM

BB

Frequency of Master Clock

Rise Time of Master Clock

Fall Time of Master Clock

Period Bit of Clock

Rise Time of Bit Clock

Fall Time of Bit Clock

Width of Master Clock High

Width of Master Clock Low

Set-Up Time from BCLK

to MCLK

Set-Up Time from FS

to MCLK

Width of Bit Clock High

Width of Bit Clock Low

Holding Time from Bit Clock

Low to Frame Sync

Holding Time from Bit Clock

High to Frame Sync

Set-Up Time for Frame Sync

to Bit Clock Low

Delay Time from BCLK

to Data Valid

Delay Time to TS

Delay Time from BCLK

Data Output Disabled

Delay Time to Valid Data from

FS

Comes Later

Set-Up Time from D

BCLK

Hold Time from BCLK

D

Set-Up Time from FS

BCLK

Hold Time from BCLK

to FS

Hold Time from 3rd Period of

Bit Clock Low to Frame Sync

(FS

Minimum Width of the Frame

Sync Pulse (Low Level)

R

e b

X

Invalid

X

or BCLK

X R

or FS

R X

X R

5 0V T

X

X

Low

Low

Low

Falling Edge

Falling Edge

Parameter

R

)

X

A

Whichever

e

X

Low

25 C All timing parameters are measured at V

R

X

X R

Valid to

R X

X R

X

X

High

X

High

Low to

to

High

Low to

Low

MCLK

MCLK

MCLK

BCLK

BCLK

MCLK

MCLK

Long Frame Only

Long Frame Only

Short Frame Only

Long Frame Only

Load

Load

C

Short Frame Sync Pulse (1 Bit Clock

Period Long)

Short Frame Sync Pulse (1 Bit Clock

Period Long)

Long Frame Sync Pulse (from 3 to 8 Bit

Clock Periods Long)

64k Bit s Operating Mode

L

e

0 pF to 150 pF

e

e

X

X

X

X

X

X

X

150 pF plus 2 LSTTL Loads

150 pF plus 2 LSTTL Loads

and BCLK

and BCLK

and MCLK

and MCLK

and MCLK

and MCLK

and MCLK

A

Conditions

7

e

R

R

R

R

R

R

R

25 C All other limits are assured by correlation with other

OH

CC

e

e a

2 0V and V

5 0V

160

160

100

100

160

160

100

100

160

Min

485

80

50

50

50

50

20

g

0

0

0

5% V

OL

e

2 048

BB

1 536

1 544

488

Typ

0 7V

e b

5 0V

15725

Max

180

140

165

165

50

50

50

50

g

5% T

CC

Units

A

MHz

MHz

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

e

e