ALC101 REALTEK, ALC101 Datasheet

ALC101

Available stocks

Related parts for ALC101

ALC101 Summary of contents

Page 1

... AC-Link ............................................................... 23 9.3 Reset..................................................................... 23 9.4 CD Input .............................................................. 24 9.5 Odd Addressed Register Access .......................... 24 9.6 Power-down Mode............................................... 24 9.7 Test Mode ............................................................ 24 9.7.1 ATE In Circuit Test Mode............................ 24 9.7.2 Vendor Specific Test Mode.......................... 24 10. Application Circuit ................................................. 25 10.1 48-pin LQFP Filter Connection Diagram .......... 25 10.2 20-pin SOP Filter Connection Diagram............. 25 11. Mechanical Dimensions .......................................... 26 11.1 LQFP-48 ............................................................ 26 11.2 SOP-20............................................................... 27 1 ALC101 Rev.1.24 ...

Page 2

... PCs. The digital interface circuitry of the ALC101 CODEC operates from a 5V/3.3V power supply with EAPD (External Amplifier Power Down) control for use in notebook and PC applications. The ALC101 integrates a 50mW/20ohm headset audio amplifier into the CODEC, saving BOM costs ...

Page 3

... Block Diagram 2001/12/5 Mixer Function Diagram: 3 ALC101 Rev.1.24 ...

Page 4

... ALC101 ALC101T ALC101 LINE-OUT-R 36 LINE-OUT AFILT2 30 AFILT1 29 Vrefout 28 Vref 27 AVss1 26 AVdd1 Rev.1.24 ...

Page 5

... Line input Left channel 13 Line input Right channel 18 Line-Out Left channel 19 Line-Out Right channel 5 ALC101 Characteristic Definition Schmitt trigger input Crystal input pad (24.576MHz / 14.318MHz) Crystal output pad Schmitt trigger input CMOS input/output Vt=0.35Vdd Schmitt trigger input CMOS output Internal pulled high (At least 20K ohm) 2mA CMOS output Internal pull high, refer to session 5 ...

Page 6

... Description (SOP-20) 14 Analog VDD (5.0V) - Analog VDD (5.0V) 15 Analog GND - Analog GND 20 Digital VDD ( 3.3V) - Digital VDD ( 3.3V) 2 Digital GND - Digital GND Pin No Description (SOP-20 Connection. 6 ALC101 Characteristic Definition Analog output Analog output (2.25V – 2.75V) 1000pf to AGND 1000pf to AGND Characteristic Definition Characteristic Definition Rev.1.24 ...

Page 7

... REF ANL DAC ADC ALC101 D1 D0 DE-FAULT ID1 ID0 5800h MR1 MR0 8000h PV0 0 8000h PH1 PH0 8008h MI1 MI0 8008h NR1 NR0 8808h CR1 CR0 8808h AR1 AR0 ...

Page 8

... Master Left Volume: (MLV[4:0]) in 1.5 dB step 7:5 - Reserved 4:0 R/W Master Right Volume: (MRV[4:0]) in 1.5 dB step For MRV/MLV: 00h 1Fh Implement 5-bit volume control only. Writing 1xxxxx will be interpreted as x11111 and when read will respond with x11111. 2001/12/5 Function Function 1: Mute (-∞ dB attenuation 46.5 dB attenuation 8 ALC101 Rev.1.24 ...

Page 9

... The purpose of this register is to allow the PC Beep signals to pass through the ALC101, eliminating the need for an external system speaker/buzzer. The PC BEEP pin is directly routed (internally hardwired) to the LINE-OUTL & R pins. If the PC speaker/buzzer is eliminated recommended to connect the external speakers at all times so the POST codes can be heard during reset ...

Page 10

... Mute Control: 0: Normal 14:13 - Reserved 12:8 R/W AUX Left Volume: ALV[4:0] in 1.5 dB steps 7:5 - Reserved 4:0 R/W AUX Right Volume: ARV[4:0] in 1.5 dB steps For ALV/ARV: 00h +12 dB Gain 08h 0dB gain 1Fh -34.5dB Gain 2001/12/5 Function 1: Mute (-∞ dB) Function 1: Mute (-∞ dB) Function 1: Mute (-∞ dB) 10 ALC101 Rev.1.24 ...

Page 11

... VIDEO LEFT (Not Supported) 3 AUX LEFT 4 LINE LEFT 5 STEREO MIXER OUTPUT LEFT 6 MONO MIXER OUTPUT 7 PHONE For RRS 0 MIC 1 CD RIGHT 2 VIDEO RIGHT (Not Supported) 3 AUX RIGHT 4 LINE RIGHT 5 STEREO MIXER OUTPUT RIGHT 6 MONO MIXER OUTPUT 7 PHONE 2001/12/5 Function 1: Mute (-∞ dB) Function 11 ALC101 Rev.1.24 ...

Page 12

... Note that the 3D bit in the general purpose register (bit 13) must be set enable this function. Bit Type 15:2 R Reserved, Read as 0 1:0 R/W Depth Control: DP[1:0] 3D effect control: DP[1:0] 2001/12/5 1: Mute (-∞ dB) 0: Off Function 00 Off (R=0KΩ) 01 33% (R=5KΩ) 10 66%(R=7.5KΩ) 11 100%(R=10KΩ) 12 Function Function Function ALC101 Rev.1.24 ...

Page 13

... R ID1, always read ID0, always read as 0. 13:12 R Reserved, Read as 0 11:10 R REV[1:0]=01 indicates that the ALC101 is AC’97 rev2.2 compliant AMAP read as 1 (DAC mapping base on CODEC ID) 8:1 - Reserved 0 R VRA read as 0 (Variable sample rate is not supported) 2001/12/5 ...

Page 14

... The two registers (MX7C Vendor ID1 and MX7E Vendor ID2) contain four 8-bit ID codes. The first three codes have been assigned by Microsoft for Plug and Play definitions. The fourth code is a Realtek assigned code identifying the ALC101. The MX7C Vendor ID1 register contains the value 414Ch, which is the first and second characters of the Microsoft ID code. The MX7C Vendor ID2 register contains the value 4730h, which is the third of the Microsoft ID code ...

Page 15

... Response Passband 0 Stopband 28.8 Stopband Rejection Passband Frequency Response 15 Typical Maximum 3.3 3.6 5.0 5.5 - +70 +125 4000V Over 5000V Typical Maximum (Dvdd=3.3v) 3.3 3.6 - Dvdd+0.30 - 0.35Dvdd - - - - 0.1DVdd - Typical Maximum - 19.2 -76.0 +- 0.15 - 19.2 -78.5 +- 0.15 ALC101 Units Units Units KHz KHz dB dB KHz KHz dB dB Rev.1.24 ...

Page 16

... Warm Reset Parameter SYNC active high pulse width SYNC inactive to BIT_CLK Startup delay 2001/12/5 Cold reset timing diagram Symbol Minimum T 1.0 rst_low T 162.8 rst2clk Warm reset timing diagram Symbol Minimum T 1.0 sync_high T 162.8 sync2clk 16 Typical Maximum - - - - Typical Maximum - - - - ALC101 Units us ns Units us ns Rev.1.24 ...

Page 17

... AC-Link Clocks The ALC101 derives its clock internally from an externally connected 24.576MHz crystal or an oscillator through the XTAL_IN pin. Synchronization with the AC’97 controller is achieved through the BIT_CLK pin at 12.288MHz (half of crystal frequency. The beginning of all audio sample packets, or “Audio Frames,” transferred over AC-Link is synchronized to the rising edge of the “ ...

Page 18

... Note: Combined rise or fall plus flight times are provided for worst case scenario modeling purpose. 2001/12/5 Data Output and Input timing diagram Symbol Minimum Symbol Minimum t 10 setup t 10 hold Symbol Minimum - - 18 Typical Maximum - 15 Typical Maximum - - - - Typical Maximum - ALC101 Units ns Units ns ns Units ns ns Rev.1.24 ...

Page 19

... Signal Rise and Fall timing diagram Symbol Minimum Trise - clk Tfall - clk Trise - sync Tfall - sync Trise - din Tfall - din Trise - dout Tfall - dout Typical Maximum - ALC101 Units Rev.1.24 ...

Page 20

... AC-Link Low Power Mode Timing The ALC101 AC-Link can be placed into low power mode by programming register 26h. Both BIT_CLK and SDATA_IN will be brought to and held at a logic low voltage level. The AC’97 controller can wake up the ALC101 by providing the proper reset signals. Parameter ...

Page 21

... This requirement is not mentioned in the AC’97 specifications Rev 2.2. Please refer to CNR (Communication Network Riser) specifications Rev.1.0 pages 23~25 or AC’97 Rev.2.2 for detailed information. 2001/12/5 ATE test mode timing diagram Symbol Minimum T 15.0 setup2rst T - off 1 CODEC 2 CODEC 55pF 62.5pF 47.5pF 55pF 21 Typical Maximum - - - 25.0 3 CODEC 4 CODEC 75pF 60pF ALC101 Units ns ns 85pF 62.5pF Rev.1.24 ...

Page 22

... C, Dvdd=3.3V ±5%,Avdd=5.0V±5% =25 Minimum 1.0 1.0 1.0 0. 19,200 28,800 - Typical Maximum 1 1 20,000 19,200 - 28,800 ∞ - - 0.8 1.0 2.25-2. ALC101 Units Vrms Vrms KΩ KΩ Ω Rev.1.24 ...

Page 23

... When the ALC101 takes serial data from the AC97 controller, it samples SDATA_OUT on the falling edge of BIT_CLK. When the ALC101 sends serial data to the AC97 controller, it starts to drive SDATA_IN on the rising edge of BIT_CLK. The ALC101 will return any uninstalled bits or registers with 0 for read operations. The ALC101 also stuffs the unimplemented slots or bits with 0 in SDATA-IN. Note that AC-LINK is MSB-justified. Refer to “ ...

Page 24

... SYNC is sampled high at the trailing edge of RESET#. At this mode ALC101 will drive BIT_CLK, SDATA_IN, EAPD and SPDIFO to high impedance. Note: To make the most compatibility with AC’97 rev2.2, ALC101 will float its digital output pins in both ATE and Vendor-Specific test mode. Please refer to AC’97 rev2.2 section 9.2 for detail description about test mode. ...

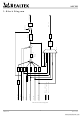

Page 25

... Off: 24.576MHz crystal or external clock +3.3V digital U14 20 XTL-IN DVDD +100u 19 DVSS LOUT-R +100u 18 SDATA_OUT LOUT BITCLK AFILT2 16 1n SDATA_IN AFILT1 15 SYNC AVSS 14 RESET# AVDD 13 1u CD-L LINE CD-GND LINE CD-R MIC ALC101T ALC101 LOUT-L LOUT-L +5VA LINE-R LINE-L MIC Rev.1.24 ...

Page 26

... APPROVE 0.354 BSC 0.276 BSC CHECK 0.217 0.354 BSC 0.276 BSC 0.217 0.007 0.008 0.011 0.016 BSC 3.5 7 0.018 0.0236 0.030 0.0393 26 TITLE: LQFP-48 (7.0x7.0x1.6mm) LEADFRAME MATERIAL DOC. NO. VERSION 02 DWG NO. PKGC-065 DATE REALTEK SEMICONDUCTOR CORP. ALC101 Rev.1.24 ...

Page 27

... SOP-20 2001/12/5 D 0.050 typ.0.016 typ. SYMBOL INCH MINIMUM TYPICAL A 0.093 - A1 0.004 - D 0.496 - E 0.291 - H 0.394 - L 0.016 - 27 ALC101 L 0.004max. MAXIMUM 0.104 0.012 0.508 0.299 0.419 0.050 Rev.1.24 ...

Page 28

... Realtek/Avance Logic, Inc. Headquarters 1F, No. 2, Industry East Road IX, Science-based Industrial Park, Hsinchu, 300, Taiwan, R.O.C. Tel : 886-3-5780211 Fax : 886-3-5776047 WWW: www.realtek.com.tw 2001/12/5 28 ALC101 Rev.1.24 ...