ISL3874AIK-TK Intersil Corporation, ISL3874AIK-TK Datasheet

ISL3874AIK-TK

Available stocks

Related parts for ISL3874AIK-TK

ISL3874AIK-TK Summary of contents

Page 1

... NUMBER RANGE ( C) PACKAGE ISL3874AIK - 192 BGA ISL3874AIK-TK - Tape and Reel 1000 Units /Reel 1 August 2001 Features • Start up modes allow the PCI and mini PCI Card Information Structure to be initialized from a serial EEPROM. This Allows Firmware to be Downloaded from the Host, Eliminating the Parallel Flash Memory Device • ...

Page 2

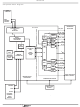

Simplified Block Diagram HOST COMPUTER DATA ADDRESS CONTROL PCI/CARD BUS 32 HOST INTERFACE MICRO- PROGRAMMED MAC ENGINE WEP ENGINE ON-CHIP ROM MEMORY CONTROLLER ON-CHIP RAM MEDIUM ACCESS CONTROLLER ADDRESS DATA SELECT EXTERNAL SRAM AND FLASH MEMORY 2 ISL3874A AGC CTL ...

Page 3

ISL3874A Signal Descriptions PIN PIN NAME NUMBER PIN I/O TYPE HAD31 A8 5V Tol, CMOS, BiDir PCI address/data bus bit 31. These signals make up the multiplexed PCI address and data bus on HAD30 A9 5V Tol, CMOS, BiDir HAD29 ...

Page 4

PIN PIN NAME NUMBER PIN I/O TYPE HBE0 H16 5V Tol, CMOS, BiDir PCI bus commands and byte enables. HBE0 applies to byte 0 (HAD7-HAD0). HINTA C6 CMOS, Output HRESET D6 5V Tol, CMOS, Input PCI reset. HFRAME B15 5V ...

Page 5

PIN NAME PIN NUMBER PL4-MA19 A4 CMOS BiDir, 2mA MA18 A3 CMOS BiDir, 2mA MA17 B4 CMOS BiDir, 2mA MA16 C3 CMOS TS Output, 2mA MA15 B3 CMOS TS Output, 2mA MA14 A1 CMOS TS Output, 2mA MA13 C2 CMOS ...

Page 6

PIN NAME PIN NUMBER MLBE L3 CMOS BiDir Output, 2mA, 50K Pull Up MOE L1 CMOS TS Output, 2mA, 50K Pull Up MWE/ MWEL L2 CMOS TS Output, 2mA, 50K Pull Up RAMCS K2 CMOS TS Output, 2mA, 50K Pull ...

Page 7

PIN NAME PIN NUMBER PJ0 P5 CMOS BiDir, 2mA, 50K Pull Up PJ1 T1 CMOS BiDir, 2mA, 50K Pull Down PJ2 R3 CMOS BiDir, 2mA, 50K Pull Down TCLKIN(CS) L4 I/O, 50K Pull Down PIN NAME PIN NUMBER XTALIN J2 ...

Page 8

PIN NAME PIN NUMBER PIN I/O TYPE GRESET L15 I TCLKIN(CS) L4 I/O, 50K Pull Down ANTSEL N15 O ANTSEL N16 O Test_Mode C4 I CompCap1 R15 I CompCap2 R13 I CompRes1 T15 I CompRes2 P13 I DBG4 B6 I/O ...

Page 9

Absolute Maximum Ratings Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 10

AC Electrical Specifications (Test conditions @ 25 PARAMETER SYNTHESIZER SYNTHCLK(PK1) Period SYNTHCLK(PK1) Width Hi SYNTHCLK(PK1) Width Lo SYNTHDATA(PK2) Hold Time from Falling Edge of SYNTHCLK(PK1) SYNTHCLK(PK1) Falling Edge to SYNLE Inactive SYSTEM INTERFACE - PCI TIMING Cycle Time, HPCLK Pulse ...

Page 11

Waveforms (Continued) ADDRESS MA(17..1) RAMCS MWE MD(15..0) SYNTHCLK SYNLE SPCSPWR t SYNTHDATA 1.5V HPCLK PCI OUTPUT PCI INPUT FIGURE 2. MAC EXTERNAL MEMORY WRITE TIMING CYC t D1 ...

Page 12

ISL3874A MD0..15 MA1..17 NVCS MOE MWEL MA0/MWEH RAMCS FIGURE 6. 8 BIT MEMORY INTERFACE ISL3874A MA1..17 MD0..15 NVCS MA0/MWEH MLBE RAMCS MOE MWEL FIGURE 7. 16-BIT MEMORY INTERFACE 12 SRAM 128Kx8 MD0..7 MA1.. SRAM 128Kx16 ADDR(0..16) DATA(0..15) ...

Page 13

LARGE SERIAL EEPROM MISO (PJ2) SD (PJ1) ISL3874A SCLK (PJ0) CS# (TCLKIN) PULLUP External Memory Interface The ISL3874A provides separate external chip selects for code space and data storage space. Code space is accessible as data space through an overlay ...

Page 14

MWEL/MWE is the only write control, and MOE is the read output enable. For 16-bit spaces constructed from 8-bit memories, the ISL3874A dynamically configures pin MA0/MWEH cycle-by- cycle as the high byte write enable, MWEL as the low write enable ...

Page 15

These are the minimum set of registers required for the card to respond to a target operation. The Memory Base Address register is used to set the starting address range this device will respond to. The maximum address space for ...

Page 16

PCI address lines on the PCI bus. HRESET - PCI Card reset signal. This reset signal only resets the PCI core. HFRAME - PCI Card FRAME cycle signal. FRAME is driven ...

Page 17

Frame ID (FID). This facilitates Power Management queuing, and allows dynamic fragmentation and defragmentation by controller. Simple Allocate/ Deallocate commands insure low host CPU overhead for memory management. Hardware buffer chaining provides high performance while reading and writing buffers. Data ...

Page 18

PE1 TX_PE PE2 t D1 PA_PE TR_SW TR_SW_BAR Master Clock Prescaler The ISL3874A contains a clock prescaler to provide flexibility in the choice of clock input frequencies. For 11Mb/s operation, the internal master clock, MCLK, must be at least 11MHz. ...

Page 19

XTALIN X1 10MΩ XTALOUT 4700pF FIGURE 10. 32.768kHz CRYSTAL MD[11], IDLE, has no equivalent functionality in any control register. When asserted at reset, it will inhibit firmware execution. This is used to allow the initial download of firmware in ...

Page 20

MD15 MD14 DEVICE TYPE 0 0 AT45DB011 0 1 24C08 (Note None NOTE: 3. The operating frequency of the serial port is 400kHz with a voltage of 3.3V. TABLE 14 A/D SPECIFICATIONS PARAMETER MIN Full ...

Page 21

The preamble is always transmitted as the DBPSK waveform while the header can be configured to be either DBPSK, or DQPSK, and data packets can be configured for DBPSK, DQPSK, or CCK. The preamble is used by the receiver to ...

Page 22

In the short preamble mode, the modem uses a synchronization field of 56 zero symbols along with an SFD transmitted at 1Mbps. The short header is transmitted at the 2Mbps rate. The synchronization preamble is all 0’s to distinguish it ...

Page 23

Scrambling is done by division with a prescribed polynomial as shown in Figure 14. A shift register holds the last quotient and the output is the exclusive or of the data and the sum of taps in the shift register. ...

Page 24

DQPSK modulation as shown in the table. The symbols of the MPDU shall be numbered starting with “0” for the first symbol for the purposes of determining odd and even symbols. That is, the MPDU starts on an even numbered ...

Page 25

RSSI against a threshold. The threshold may be set to an absolute power value may be set above the measured noise floor. See CR35. The ISL3874A measures and stores the RSSI level ...

Page 26

ISL3874A from the HFA3783 chip. A '1' indicates its inputs are near saturation and it needs the RF chip to switch from high gain to low gain. RX_IF_Det is the input to the ...

Page 27

SQ1s will cause the part to finish the acquisition phase and enter the tracking phase. Prior to initial acquisition the NCO is inactive (0Hz) and carrier phase measurement are done on a symbol by symbol basis. After acquisition, coherent ...

Page 28

Secondly, when the bits are processed by the descrambler, these errors are further extended. The descrambler is a 7-bit shift register ...

Page 29

V (ANALOG) DD RX_IF_DET RX_IF_AGC CONTROL 6-BIT RX-RF-AGC DAC DIVERSITY ANT SEL CONTROL 6-BIT RXI A/D 6 6-BIT RXQ A/D 6 COHERENT TIMING INTEGRATOR ANTENNA ANTSEL SWITCH ANTSEL CONTROL TIMING GENERATOR MCLK RESET RX_PE FIGURE 18. DSSS BASEBAND PROCESSOR, RECEIVE ...

Page 30

Data Demodulation in the CCK Modes In this mode, the demodulator uses Complementary Code Keying (CCK) modulation for the two highest data rates slaved to the low rate processor which it depends on for acquisition of initial timing ...

Page 31

CCK modes. The losses in both figures include RF and IF radio losses; they do not reflect the ISL3874A losses alone. The ISL3874A baseband processing losses from theoretical are, by themselves, a small percentage of the overall ...

Page 32

Signal Quality Estimate A signal quality measure is available on CR51 for use by the MAC. This measure is the SNR in the carrier tracking loop and can be used to determine when the demodulator is working near to the ...

Page 33

Control Registers The following tables describe the function of each control register along with the associated bits in each control register. CONFIGURATION REGISTER 0 ADDRESS (0h) R PART/VERSION CODE Bit 7:4 Part Code 3 = HFA3863 series Bit 3:0 Version ...

Page 34

CONFIGURATION REGISTER 5 ADDRESS (0Ah) R/W TX SIGNAL FIELD Bits 7:5 R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions. Bit 4 TX/RX filter / CMF weight select US. 1 ...

Page 35

CONFIGURATION REGISTER 10 ADDRESS (14h) R/W RX CONFIGURE Bit 7 AGC freeze during packet Disable (do not disable unless MAC can handle baseband processor aborting during MPDU reception Enable. Bit 6 CIR estimate/ Dot product clock ...

Page 36

CONFIGURATION REGISTER 12 ADDRESS (18h) R/W A/D TEST MODES 1 (Continued) Bit 3 Q DAC clock enable disable. Bit 2 RF A/D clock enable disable. Bit 1 I A/D clock ...

Page 37

CONFIGURATION REGISTER 14 ADDRESS (1Ch) R/W A/D TEST MODES 3 (Continued) Bit 3 Enable test bus into RX and TX DAC (if below bit normal enable. Bit 2 Enable RF A/D into RX ...

Page 38

CONFIGURATION REGISTER 23 ADDRESS (2Eh) R/W AGC TABLE DATA Bits 7 R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions. Bits 6:0 AGC look up table data, unsigned. CONFIGURATION REGISTER 24 ADDRESS ...

Page 39

CONFIGURATION REGISTER ADDRESS 30 (3Ch) R/W CARRIER SENSE 2 SCALE FACTOR Bits 7:6 R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions. Bit 5:0 Carrier Sense 2 (CS2) scale factor (0-7.875 range) ...

Page 40

CONFIGURATION REGISTER ADDRESS 33 (42h) R/W TEST MODES 2 (Continued) Bit 2 Internal digital loop back mode (SDI pin becomes LOCK input to acquisition block normal chip operation loop back disabled loop back enabled, A/D and ...

Page 41

CONFIGURATION REGISTER ADDRESS 41 (52h) R/W PREAMBLE/HEADER LEAD COEFFICIENT Bit 7:6 R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions. Bit 5:0 Preamble Lead Coefficient (0-4 range) (000000 - 100000). CONFIGURATION REGISTER ...

Page 42

CONFIGURATION REGISTER ADDRESS 51 (66h) R SIGNAL QUALITY MEASURE Bit 7:0 a: NOISEfloorAntA [7:0] unsigned, range 0-255. b: measures signal quality based on the SNR in the carrier tracking loop. CONFIGURATION REGISTER ADDRESS 52 (68h) R RECEIVED SIGNAL FIELD Bit ...

Page 43

Bit 7:0 a&b: 8-bit value of Packet RSSI, unsigned, range 0 to 255 dB. CONFIGURATION REGISTER ADDRESS 63 (80h) R RECEIVE STATUS Bit 7:6 a&b: signal field value (HRfieldmatch/QPSKwd_OK 5. ...

Page 44

... Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. ...