HFA3863IV Intersil Corporation, HFA3863IV Datasheet - Page 28

HFA3863IV

Manufacturer Part Number

HFA3863IV

Description

Direct Sequence Spread Spectrum Baseband Processor with Rake Receiver and Equalizer

Manufacturer

Intersil Corporation

Datasheet

1.HFA3863IV.pdf

(39 pages)

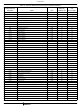

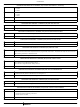

Bit 3

Bit 2

Bit 1

Bit 0

Bit 7

Bits 6:0

Bits 7:4

Bits 3:0

Bit 7:6

Bit 5:0

Bits 7:4

Bits 3:0

Bits 7:5

Bits 4:0

Bits 7:5

Bit 4:0

Bits 7,6

Bits 5:0

Bits 7,6

Bits 5

Bits 4:0

Enable test bus into RX and TX DAC (if below bit 2 is 0).

0 = normal.

1 = enable.

Enable RF A/D into RX DAC.

0 = normal.

1 = enable.

VRbit1.

VRbit0.

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

AGC gain clip (7-bit value, 0-127) this is the attenuator accumulator upper limit. The lower limit is 0.

AGC mid Saturation counts (0–15 range) these are the counts to kick in the low and mid attenuator steps (CR28).

AGC low Saturation Count (0–15 range).

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

RXRF_AGC pad value to use in the RSSI calculation, Range 0–63dB (nominally 30dB).

AGC high saturation attenuation value (0–30).

NOTE: hi saturation attenuation step actual value is programmed value times 2. This attenuation step will occur if the # of I

and Q sats is greater than hi saturation count.

AGC hi sat count (0–15 range).

CW detector scale multiplication factor. (xxxx.x). See CR35 and CR 49.

Set to 00h for forcing CW detect always active.

Set to 0Fh for forcing CW detector always inactive.

AGC Lock-in level (0–7.5 range). Note this is the inner lock window.

AGC max lock count for antenna search. The number of updates required to lock AGC must be less than or equal to this count

for antenna diversity search to be allowed to run. Range 0 to 7.

AGC Lock Window positive side (0–15.5 range). Note: this is the outer lock window.

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

AGC Backoff (xxxxx.x, 0–31.5 range) in half dB steps. This sets the operating headroom in the I and Q ADCs.

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

AGC Look up table read control bit.

1 = Read AGC table at address given below.

0 = Read contents of CR23.

AGC lookup table address (32 address bits).

CONFIGURATION REGISTER 14 ADDRESS (1Ch) R/W A/D TEST MODES 3 (Continued)

CONFIGURATION REGISTER 22 ADDRESS (2Ch) R/W AGC LOOKUP TABLE ADDRESS

CONFIGURATION REGISTER 16 ADDRESS (20h) R/W AGC SATURATION COUNTS

CONFIGURATION REGISTER 20 ADDRESS (28h) R/W AGC LOCK WINDOW POS.

28

CONFIGURATION REGISTER 19 ADDRESS (26h) R/W AGC LOCK IN LEVEL

CONFIGURATION REGISTER 17 ADDRESS (22h) R/W AGC RF PAD VALUE

CONFIGURATION REGISTER 15 ADDRESS (1Eh) R/W AGC GAIN CLIP

CONFIGURATION REGISTER 21 ADDRESS (2Ah) R/W AGC BACKOFF

CONFIGURATION REGISTER 18 ADDRESS (24h) R/W AGC HI SAT

HFA3863