ADC12034 National Semiconductor Corporation, ADC12034 Datasheet - Page 31

ADC12034

Manufacturer Part Number

ADC12034

Description

Self-calibrating 12-bit Plus Sign Serial I/o A/d Converters With Mux And Sample/hold

Manufacturer

National Semiconductor Corporation

Datasheet

1.ADC12034.pdf

(44 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ADC12034CIMSA

Manufacturer:

NS/国半

Quantity:

20 000

Part Number:

ADC12034CIWM

Manufacturer:

NS/国半

Quantity:

20 000

Applications Information

Some of the device/package combinations are obsolete

and are described here for reference only. Please see our

web site for availability.

1.0 DIGITAL INTERFACE

1.1 Interface Concepts

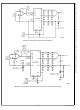

The example in Figure 7 shows a typical sequence of events

after the power is applied to the ADC12030/2/4/8:

The first instruction input to the A/D via DI initiates Auto-Cal.

The data output on DO at that time is meaningless and is

completely random. To determine whether the Auto Cal has

been completed, a read status instruction is issued to the A/

D. Again the data output at that time has no significance since

the Auto Cal procedure modifies the data in the output shift

register. To retrieve the status information, an additional read

status instruction is issued to the A/D. At this time the status

data is available on DO. If the Cal signal in the status word,

is low Auto Cal has been completed. Therefore, the next in-

struction issued can start a conversion. The data output at this

time is again status information. To keep noise from corrupt-

ing the A/D conversion, status can not be read during a

conversion. If CS is strobed and is brought low during a con-

version, that conversion is prematurely ended. EOC can be

used to determine the end of a conversion or the A/D con-

troller can keep track in software of when it would be appro-

priate to communicate to the A/D again. Once it has been

determined that the A/D has completed a conversion, another

instruction can be transmitted to the A/D. The data from this

conversion can be accessed when the next instruction is is-

sued to the A/D.

Note, when CS is low continuously it is important to transmit

the exact number of SCLK cycles, as shown in the timing di-

agrams. Not doing so will desynchronize the serial commu-

nication to the A/D. (See Section 1.3.)

1.2 Changing Configuration

The configuration of the ADC12030/2/4/8 on power up de-

faults to 12-bit plus sign resolution, 12- or 13-bit MSB First,

10 CCLK acquisition time, user mode, no Auto Cal, no Auto

Zero, and power up mode. Changing the acquisition time and

turning the sign bit on and off requires an 8-bit instruction to

be issued to the ADC. This instruction will not start a conver-

sion. The instructions that select a multiplexer address and

format the output data do start a conversion. Figure 8 de-

scribes an example of changing the configuration of the

ADC12030/2/4/8.

During I/O sequence 1, the instruction on DI configures the

ADC12030/2/4/8 to do a conversion with 12-bit +sign resolu-

tion. Notice that when the 6 CCLK Acquisition and Data Out

without Sign instructions are issued to the ADC, I/O se-

quences 2 and 3, a new conversion is not started. The data

output during these instructions is from conversion N which

was started during I/O sequence 1. The Configuration Modi-

fication timing diagram describes in detail the sequence of

FIGURE 7. Typical Power Supply Power Up Sequence

1135436

31

events necessary for a Data Out without Sign, Data Out with

Sign, or 6/10/18/34 CCLK Acquisition time mode selection.

Table 5 describes the actual data necessary to be input to the

ADC to accomplish this configuration modification. The next

instruction, shown in Figure 8, issued to the A/D starts con-

version N+1 with 8 bits of resolution formatted MSB first.

Again the data output during this I/O cycle is the data from

conversion N.

The number of SCLKs applied to the A/D during any conver-

sion I/O sequence should vary in accord with the data out

word format chosen during the previous conversion I/O se-

quence. The various formats and resolutions available are

shown in Table 1. In Figure 8, since 8-bit, without sign, MSB

first format was chosen during I/O sequence 4, the number of

SCLKs required during I/O sequence 5 is 8. In the following

I/O sequence the format changes to 12-bit without sign MSB

first; therefore the number of SCLKs required during I/O se-

quence 6 changes accordingly to 12.

1.3 CS Low Continuously Considerations

When CS is continuously low, it is important to transmit the

exact number of SCLK pulses that the ADC expects. Not do-

ing so will desynchronize the serial communications to the

ADC. When the supply power is first applied to the ADC, it will

expect to see 13 SCLK pulses for each I/O transmission. The

number of SCLK pulses that the ADC expects to see is the

same as the digital output word length. The digital output word

length is controlled by the Data Out (DO) format. The DO for-

mat maybe changed any time a conversion is started or when

the sign bit is turned on or off. The table below details out the

number of clock periods required for different DO formats:

If erroneous SCLK pulses desynchronize communications,

the simplest way to recover is by cycling the power supply to

the device. Not being able to easily resynchronize the device

is a shortcoming of leaving CS low continuously.

The number of clock pulses required for an I/O exchange may

be different for the case when CS is left low continuously vs.

the case when CS is cycled. Take the I/O sequence detailed

in Figure 7 (Typical Power Supply Sequence) as an example.

The table below lists the number of SCLK pulses required for

each instruction:

1.4 Analog Input Channel Selection

The data input on DI also selects the channel configuration

(see Tables 2, 3, 4, 5). In Figure 8 the only times when the

12-Bit MSB or LSB First

16-Bit MSB or LSB first

Auto Cal

Read Status

Read Status

12-Bit + Sign Conv 1

12-Bit + Sign Conv 2

8-Bit MSB or LSB First

Instruction

DO Format

Continuously

13 SCLKs

13 SCLKs

13 SCLKs

13 SCLKs

13 SCLKs

SIGN OFF

SIGN ON

SIGN OFF

SIGN ON

SIGN OFF

SIGN ON

CS Low

CS Strobed

Number of

13 SCLKs

Expected

8 SCLKs

8 SCLKs

8 SCLKs

8 SCLKs

www.national.com

SCLKs

12

13

16

17

8

9