lmx2505lq1321 National Semiconductor Corporation, lmx2505lq1321 Datasheet - Page 9

lmx2505lq1321

Manufacturer Part Number

lmx2505lq1321

Description

Pllatinu Dual Frequency Synthesizer System With Integrated Vcos

Manufacturer

National Semiconductor Corporation

Datasheet

1.LMX2505LQ1321.pdf

(16 pages)

Functional Description

BAND SELECT MODE

The BS pin and BS bit can be used to select one of the two

RF VCO outputs. When using the BS pin, the BS bit must be

set to 0, and when using the BS bit, the BS pin must be tied

to ground. When using the BS pin, the state of the input must

exceed the minimum band select set up time prior to the LE

signal transition. The truth table summarizing the band select

logic is as follows:

LOCK DETECT MODE

The LD output can be used to indicate the lock status of the

PLL. Bit 6 in Register R1 determines the signal that appears

Note 14: LD output becomes LOW when the phase error is larger than t

Note 15: LD output becomes HIGH when the phase error is less than t

four or more consecutive cycles.

Note 16: Phase Error is measured on leading edge. Only errors greater than

t

W1

and t

BS Pin

HIGH

W2

LOW

LOW

are labeled.

TABLE 2. Band Select Modes

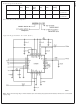

FIGURE 2. Lock Detect Timing Diagram Waveform (Notes 14, 15, 16, 17, 18)

BS Bit

0

0

1

(Continued)

PDC1500

PDC1500

PDC800

Mode

W1

W2

for

.

9

on the LD pin. When the PLL is not locked, the LD pin

remains LOW. After obtaining phase lock, the LD pin will

have a logical HIGH level. The LD output is always LOW

when the LD register bit is 0 and in power down mode.

Note 17: t

both bands.

Note 18: The lock detect comparison occurs with every 64

f

N

.

RF PLL Section

W1

Not Locked

Locked

LD Bit

is 5 ns for PDC1500 and 10 ns for PDC800. t

TABLE 3. Lock Detect Modes

0

1

TABLE 4. Lock Detect Logic

Disable (GND)

LD Output

Enable

Mode

HIGH

LOW

20067108

th

W2

cycle of f

www.national.com

is 10 ns for

R

and