ca3304 Intersil Corporation, ca3304 Datasheet

ca3304

Available stocks

Related parts for ca3304

ca3304 Summary of contents

Page 1

... The overflow bit makes possible the connection of two or more CA3304s in series to increase the resolution of the conversion system. A series connection of two CA3304s may be used to pro- duce a 5-bit, 25MHz converter. Operation of two CA3304s in parallel doubles the conversion speed (i.e., increases the sampling rate from 25MHz to 50MHz) ...

Page 2

... Voltage Range . . . . . . . V AA Operating Temperature CA3304D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55 CA3304E, CA3304M -40 CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. ...

Page 3

... Input current is due to energy transferred to the input at the start of the sample period. The average value is dependent on input and V DD voltage. 3. The CLK input is a CMOS inverter with a 50k feedback resistor. It operates from the V with a 1V minimum source. P-P 4. Parameter not tested, but guaranteed by design or characterization. CA3304, CA3304A 2V 5V ...

Page 4

... NOTE: 1. The voltages listed are the ideal centers of each output code shown as a function of its associated reference voltage See Ideal Transfer Curve Figure 6. The output code should exist for an input equal to the ideal center voltage CA3304, CA3304A Bit 1 (LSB). Bit 2. Bit 3. ...

Page 5

... NOTE: CE1 and CE2 inputs and data outputs have standard CMOS protection networks to V standard CMOS protection networks Timing Diagrams DATA SHIFTED INTO OUTPUT REGISTERS AUTO 1 BALANCE CLOCK B4, DC & CE1 CE2 BITS 1-4 DC, OF CA3304, CA3304A 2 OUTPUT REGISTER COUNT LATCH ...

Page 6

... With 2 as standby state (indefinite standby, lower power than 3B) Typical Performance Curves -50 - TEMPERATURE ( FIGURE 4. DATA DELAY vs TEMPERATURE CA3304, CA3304A 2 CLOCK NEW DATA OUTPUT With 1 as standby state (indefinite standby, double pulse needed) SAMPLE ENDS OLD DATA INVALID DATA FIGURE 3C ...

Page 7

... TEMPERATURE ( FIGURE 6. NON-LINEARITY vs TEMPERATURE 0.50 0.45 0.40 0.35 0.30 0.25 0.20 0.15 0.10 0.05 0. (MHz) S FIGURE 8. NON-LINEARITY vs SAMPLE FREQUENCY 4.00 3.80 3.60 3.40 3.20 3.00 2.80 2.60 2.40 2.20 2. (MHz) I FIGURE 10. EFFECTIVE BITS vs INPUT FREQUENCY CA3304, CA3304A (Continued) 0.10 0.09 0.08 0.07 INL 0.06 0.05 DNL 0.04 0.03 0.02 0.01 0. FIGURE 7. NON-LINEARITY vs REFERENCE VOLTAGE 4.00 3.80 3.60 3.40 INL 3.20 3.00 2.80 2.60 2.40 2.20 DNL 2. -40 -30 FIGURE 9. EFFECTIVE BITS vs TEMPERATURE 7 ...

Page 8

... Typical Performance Curves 2V REFERENCE REMOTE 2V INTO 50 SOURCE FIGURE 12A. TYPICAL CA3304 UNIPOLAR CIRCUIT CONFIGURATION +1V REFERENCE REMOTE 1V INTO 50 SOURCE ANALOG GROUND FIGURE 12B. TYPICAL CA3304 BIPOLAR CIRCUIT CONFIGURATION CA3304, CA3304A (Continued) 27 CA3304 0.1 F CE2 4.7 F TAN CER V + REF + 0.1 F 4.7 F TAN CER DC, OF, ...

Page 9

... The conversion process now takes 60ns. [Note that the above numbers do not include the t Increased Accuracy In most case the accuracy of the CA3304 should be sufficient without any adjustments. In applications where accuracy is of utmost importance, two adjustments can be made to obtain better accuracy; i.e., offset trim and gain trim. ...

Page 10

... If the supply is noisy, decouple V + with a resistor as shown in Figure 12A. AA The CA3304 outputs current spikes to its input at the start of the auto-balance and sample clock phases. A low impedance source, such as a locally-terminated 50 cable, should be used to drive the input terminal. A fast- settling buffer such as the HA-5033, HA-5242, or CA3450 should be used if the source is high impedance ...

Page 11

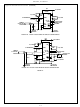

... No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries. For information regarding Intersil Corporation and its products, see web site http://www.intersil.com CA3304, CA3304A +FULL SCALE REF. BUFFER INPUT FIGURE 13. TYPICAL CA3304 5-BIT CONFIGURATION OVERFLOW ...