saa7392 NXP Semiconductors, saa7392 Datasheet

saa7392

Available stocks

Related parts for saa7392

saa7392 Summary of contents

Page 1

... DATA SHEET SAA7392 Channel encoder/decoder CDR60 Preliminary specification File under Integrated Circuits, IC01 INTEGRATED CIRCUITS 2000 Mar 21 ...

Page 2

... Operating in CLV Mode, Synchronous Stream Operation 11 PACKAGE OUTLINE 12 SOLDERING 12.1 Introduction to soldering surface mount packages 12.2 Reflow soldering 12.3 Wave soldering 12.4 Manual soldering 12.5 Suitability of surface mount IC packages for wave and reflow soldering methods 13 DEFINITIONS 14 LIFE SUPPORT APPLICATIONS 15 PURCHASE OF PHILIPS I 2 Preliminary specification SAA7392 2 C COMPONENTS ...

Page 3

... This interface can be accessed either via a parallel (80C51 serial (I PARAMETER 3.0 3.0 3 PACKAGE DESCRIPTION 3 Preliminary specification MIN. TYP. MAX. 3.3 3.6 3.3 3.6 3.3 3.6 200 8.4672 33 70 +125 12 1.4 mm SAA7392 2 C-bus) interface. UNIT MHz C C VERSION SOT315-1 ...

Page 4

... AGCREF CL1 HREFMID HIN MEAS1 W441 XEFM EFMDATA LASERON EFM CLOCK EFM ENCODE GENERATOR MODULATOR CONTROL ERROR CORRECTOR AND MEMORY PROCESSOR SAA7392 DE-MODULATOR TEST SUB-CPU INTERFACE RESET GENERATOR CONTROL XTLO PORE TEST2 TEST1 ...

Page 5

... HREFHI 10 HREFLO 11 AGCREF 12 HIN 13 HREFMID 14 V DDA2 15 V SSA2 16 TEST1 17 TEST2 18 V SSD 19 V DDE 20 2000 Mar 21 SAA7392 Fig.2 Pin configuration. 5 Preliminary specification SAA7392 60 WCLK 59 DATAO FLAG 58 57 SYNC 56 EBUOUT STOPCK 53 V DDD 52 V SSD 51 PCAin 50 CSi 49 V DDD 48 ...

Page 6

... V supply voltage; note 2 supply core and pad ring ground I sub-CPU clock I/O bidirectional sub-CPU data O sub-CPU interrupt I/O bidirectional sub-CPU parallel data bus I/O bidirectional sub-CPU parallel data bus I/O bidirectional sub-CPU parallel data bus I/O bidirectional sub-CPU parallel data bus 6 Preliminary specification SAA7392 DESCRIPTION ...

Page 7

... V supply voltage I/O motor output 2/tacho input 3 O motor control output 1 O laser write control O EFM clock output O EFM data output O front end telemetry; open-drain and V ) must be connected to the same external supply. DDA DDD 7 Preliminary specification SAA7392 DESCRIPTION ...

Page 8

... Send STOP condition. 7.1.2 The parallel interface has a multiplexed address/data bus. Information can be written to or read from the SAA7392 using the protocols shown in Figs 3 and 4; specific timings are shown in Table 2. Note that only the lower six address bits are decoded; so writing to address 40H would have the same effect as writing to address 00H ...

Page 9

... IN OUT t su1 t h2 Fig.4 Microprocessor read protocol. DESCRIPTION 9 Preliminary specification MGR794 (1) (1) MIN. MAX clk clk clk clk clk 128 clk SAA7392 UNIT ...

Page 10

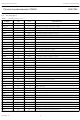

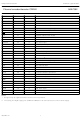

Acrobat reader. white to force landscape pages to be ... 7.2 Register map Table 3 Register map ADDRESS REGISTER NAME (HEX) 00 PLL Lock ...

Page 11

Acrobat reader. white to force landscape pages to be ... ADDRESS REGISTER NAME (HEX) 12 Clock Preset Register (ClockPre) 13 Decoder Mode Select Register ...

Page 12

Acrobat reader. white to force landscape pages to be ... ADDRESS REGISTER NAME (HEX) 2D ATIP Data End Register (ATIPDataEnd) 2E Wobble Peak Status ...

Page 13

... Sema1 and microcontroller 2 can write data to microcontroller 1 via Sema2. The Status Register of the SAA7392 offers a mechanism so that both microcontrollers can see when new data has been written and when it has been read by looking at the contents of the Semaphore Registers. Version M3 of the CDR60 can be identified by writing and reading register Sema3 ...

Page 14

... When set the offset between QSync and ATIPSync is more than 2 EFM frames different from the programmed value. 2000 Mar LockInEn HeaderValen MotorOverflowEn DESCRIPTION QSync ATIPSync DESCRIPTION 14 Preliminary specification SAA7392 2 1 FIFOOvEn 2 1 LaserOn LaserOff XErrorLarge 0 0 ...

Page 15

... After programming the BCLK clock 2. When switching from encode to decode 3. When switching from decode to encode. 2000 Mar QSyncEn ATIPSyncEn OFT ESET Preliminary specification 2 1 LaserOnEn LaserOffEn DESCRIPTION 2 1 DESCRIPTION SAA7392 0 XErrorLarge En 0 SReset1 ...

Page 16

... Channel encoder/decoder CDR60 7.3 System clocks The principle clocks used in the SAA7392 are derived from the crystal oscillator input pin XTLI (alternatively, an external clock can be connected to this pin). These clocks are the system clock (also used as the ADC clock) and the I bit clock (BCLK). ...

Page 17

... XTLI XTLI XTLI 17 Preliminary specification Div2.2 Div2.1 DESCRIPTION CL1Div = 1, then CL1 output 3 clk ); see Table 19. This frequency clk ); see Table 20 the responsibility of BCLK ) clk BCLK FREQUENCY (f ) BCLK SAA7392 0 Div2 CD) ...

Page 18

... Philips Semiconductors Channel encoder/decoder CDR60 7.4 HF analog front-end The HF ADC in the SAA7392 encodes the EFM high frequency signal from the disc light pen assembly. These signals are pre-processed, externally to the SAA7392, by either AEGER DALAS equivalent. The dynamic range of the ADC is optimized by the inclusion coupled AGC function under digital control ...

Page 19

... NOISE DIGITAL FILTER EQUALIZER SLICE LEVEL DETERMINE clocked on PLL clock DIGITAL PLL Fig.6 Block diagram of bit recovery block. 19 Preliminary specification VITERBI DETECTOR ZERO TRANS DETECTOR MULTIPLEXER RMS JITTER jitter value MEASUREMENT PLL frequency slice level SAA7392 MEAS1 MGR796 ...

Page 20

... Internal lock flags: The internally generated inner-lock signal (f_lock_in), lock signal (lock_in) and flag that indicates when a run length 14 is detected (long_symbol) are available via register PLLEqu. handbook, halfpage amplitude (dB) 20 Preliminary specification SAA7392 2 8192 frequency (Hz) Fig.7 PLL bode diagram. MGR797 ...

Page 21

... Fig.8 Format on MEAS1 pin. 2000 Mar 21 FUNCTION bit 2 bit 3 data bits MGR798 21 Preliminary specification SAA7392 ...

Page 22

... PLL into outer-lock 1 0 force PLL into inner-lock 0 0 force PLL into Hold mode (PLL frequency can be forced using preset value in register PLLFreq all other combinations are reserved 22 Preliminary specification SAA7392 2 1 PLLFreq.2 PLLFreq.1 PHASE OVERRIDE PLL LOCK 0 PLLFreq.0 ...

Page 23

... 945 This value is reserved. 2000 Mar 21 PLLFreq<7:0> ADC clock (Hz) (Hz) = ----------------------------------------------------------------------------------------- - 128 R (PLLS ) EGISTER IntegF0.1 IntegF0.0 PLLBWF1.1 PLLAsym.4 PLLAsym.3 SLICER BANDWIDTH INTEGRATOR CROSSOVER FREQUENCY 23 Preliminary specification DESCRIPTION PLLBWF1.0 LPBWF2.1 PLLAsym.2 PLLAsym.1 DESCRIPTION SAA7392 0 LPBWF2.0 PLLAsym.0 ...

Page 24

... The absolute clock jitter value can be calculated as follows: PLL clock recovery jitter % 2000 Mar 21 PLL BANDWIDTH LOW-PASS BANDWIDTH R (PLLF ) EGISTER REQ PLLFreq.6 PLLFreq.5 JV.5 JV.4 JV.3 PLLFreq<9:0> 5 – ------------------------------------- - + clk 512 JV<7:0> 6.5 ----------------------------------- - = 24 Preliminary specification 2 1 PLLFreq.4 PLLFreq.3 JV.2 JV.1 DESCRIPTION DESCRIPTION – 100 2048 SAA7392 0 PLLFreq.2 JV.0 ...

Page 25

... If Inlock = 1, then PLL is in lock. 2000 Mar 21 R (PLLE ) EGISTER Tap a1.2 Tap a1.1 Tap a1.0 Tap a1 EQUALIZER TAP SETTINGS Tap a2 0.0625 0 0.125 1 0.1875 0 0.25 1 0.3125 X All other settings are reserved. 25 Preliminary specification Tap a2.2 Tap a2.1 LongSymb FLock DESCRIPTION DESCRIPTION SAA7392 0 Tap a2.0 InLock ...

Page 26

... This is a dual-function register. When read Motor2 gives an indication of the EYE opening of the equalised HF. Table 44 Eye Open Register (address 0DH) - READ 7 6 EOV.7 EOV.6 2000 Mar 21 R (PLLFM ) EGISTER EAS 5 4 EFMns.5 EFMns.4 EFMns OTOR 5 4 EOV.5 EOV.4 EOV.3 26 Preliminary specification EFMns.2 EFMns.1 DESCRIPTION EOV.2 EOV.1 SAA7392 0 EFMns.0 0 EOV.0 ...

Page 27

... Elsif (count > maxcount): reset count. Stepsize and maxcount can be set by writing to the VitSet register reset of the counter the slice level is also reset RL2PB WDog DESCRIPTION WATCHDOG COUNT STEP OTOR 27 Preliminary specification SAA7392 2 1 MaxCnt WDogCnt 128 256 8 0 WDogCnt.0 ...

Page 28

... Euclidean algorithm logic 0 pause bit bit 0 bit 1 bit 2 start pause data bits bit Fig.9 Format on CFLG pin. SAA7392 0 ASCV.0 bit 3 MGR798 ...

Page 29

... Hold mode. Data into output FIFO is stopped (header/subheader decoding remains operative). Encode mode. All other combinations reserved. (C1BLER C2BLER) AND 5 4 C1BLER.4 C1BLER C2BLER.4 C2BLER.3 29 Preliminary specification Mode.1 Mode.0 DESCRIPTION DECODER MODE C1BLER.2 C1BLER C2BLER.2 C2BLER.1 SAA7392 0 LWCon 0 C1BLER.0 0 C2BLER.0 ...

Page 30

... After finishing the subcode read the microprocessor must release the interface by issuing a read to the dummy register SubReadEnd (no data can be read from it); this allows the SAA7392 to capture new subcode frames. The serial subcode is output on the V4 pin as illustrated in Fig.10. The subcode sync word is formed by ...

Page 31

... EAD ND EGISTER After finishing a subcode read, the microprocessor must release the interface to allow the SAA7392 to capture new subcode frames. This is done by issuing a read to SubReadEnd. No data can be read from this register; only the side effect is important. Table 58 Subcode Read End Register (address 14H) - READ ...

Page 32

... If EBUClkSelect = 0, then the EBU clock frequency is EBUClkSelect = 1, then the EBU clock frequency is MUXSWI must be a logic 1 for this setting). These 4 bits are reserved. See Section 7.11.1. 32 Preliminary specification WCLK ScramOn InputFmt.1 DESCRIPTION 2 / SAA7392 0 InputFmt XTLI f (input 3 XTLI ...

Page 33

... Bits copied from register Output2. Bit 2 is logic 1 when copy permitted. Bit 3 is logic 1 when recording has pre-emphasis CD: bit 8 = logic 1, all other bits = logic 0 set by register Output2 level level level III always zero 33 Preliminary specification DESCRIPTION DESCRIPTION SAA7392 ...

Page 34

... Fig.11 Format 1: 16 clocks/word I D15 D14 D13 D12 D11 D10 FLAG - MSB (1 is unreliable) right 34 Preliminary specification D15 D14 FLAG - LSB right MGR800 2 S format D15 D14 FLAG - LSB left MGR801 SAA7392 ...

Page 35

... Fig.14 Format 4: 24 clocks/word ‘S’ format (WCLK inverted). 2000 Mar Fig.13 Format 3: 24 clocks/word I D15 D14 D13 D12 D11 D10 D9 35 Preliminary specification SAA7392 D1 D0 FLAG - LSB 2 S format FLAG - LSB ...

Page 36

Acrobat reader. white to force landscape pages to be ... BCLK DATA D15 D14 D13 D12 D11 D10 FLAG FLAG - ...

Page 37

... These 4 bits are copied to bits the IEC958 control channel (data/audio, copy protect, de-emphasis); see Table 62. 2000 Mar 21 1) UTPUT 5 4 Format.0 WClkIO BClkIO Format UTPUT 5 4 EBUCon.28 EBUCon.3 37 Preliminary specification DESCRIPTION FORMAT Format 1 Format 2 Format 3 Format 4 Format 5 Format EBUCon.2 EBUCon.1 DESCRIPTION SAA7392 0 0 EBUCon.0 ...

Page 38

... KillEBUOn When KillEBUOn = 0, then in normal mode. When KillEBUOn = 1, then all data in IEC958/EBU channel is set to zero 0 This bit is reserved. 2000 Mar 21 3) UTPUT 5 4 InterpOn FlagPin 38 Preliminary specification KillDataOn KillEBUOn DESCRIPTION 2 S/S format output; (use for SAA7392 0 2 S/S ...

Page 39

... Motor control The spindle motor is controlled by a fully integrated digital servo sub-system within the SAA7392. Information from the data FIFO, data recovery PLL and tacho inputs may be used to calculate the motor control output signals. The frequency set-point, the FIFO settings and coefficients G, K control registers ...

Page 40

... Table 74. i has been added. This is set by writing to register Motor7. The i is then the K set by Motor2 multiplied by the K i(tot see Table 75. f G.0 0 8.36 1 10.4 0 16.7 1 20.9 0 33.4 1 41.8 0 66.9 1 83.6 40 Preliminary specification ADC clock MFS.2 MFS Kf.2 Kf.1 DESCRIPTION set by Motor7. i’ COEFFICIENT G SAA7392 0 MFS.0 0 Kf.0 ...

Page 41

... Ki’.1 DESCRIPTION coefficient; see Table 78. f’ every sample of the input is f’ of 0.5 every 2nd sample is f’ K combinations with the same product will not f’ , where the sampling in the f’ coefficient; see Table 78. i’ SAA7392 0 Ki’.0 ...

Page 42

... OTOR 8. ADC clock --------------------------- - 128 5 4 HFSP.5 HFSP.4 HFSP.3 TachoFreq.4 TachoFreq.3 These 8 bits indicate the Tacho frequency (2’s complement notation). 42 Preliminary specification COEFFICIENTS K AND K f’ i’ HFSP.2 HFSP.1 TachoFreq.2 TachoFreq.1 DESCRIPTION SAA7392 (1) (2) 0 HFSP.0 TachoFreq.0 ...

Page 43

... Motor start at 75% power Motor start at 100% power Motor stop at 37% power Motor stop at 50% power Motor stop at 75% power Motor stop at 100% power. 43 Preliminary specification SAA7392 2 1 MSCON.2 MSCON.1 MSCON.0 MOTOR SERVO STATE 0 ...

Page 44

... AND 5 4 MIV.5 MIV.4 MIV MIV.13 MIV.12 MIV. ACHO 5 4 KTacho.5 KTacho.4 KTacho ACHO 5 4 TIntF.5 TIntF.4 TIntF.3 44 Preliminary specification MIV.2 MIV MIV.10 MIV KTacho.2 KTacho TIntF.2 TIntF.1 SAA7392 0 MIV.0 0 MIV.8 0 KTacho.0 0 TIntF.0 ...

Page 45

... This value is reserved Motor servo runs on tacho frequency This value is reserved. 2000 Mar ACHO 5 4 Moto2/T3 Fsam Fsam<1:0> system clock Hz = ---------------------------------------------------------------------------------- - 32768 MOTOR SERVO FREQUENCY SOURCE 45 Preliminary specification Fsam.0 TachoIntLF DESCRIPTION ) as shown below: s SAA7392 0 TachoMode ...

Page 46

... CD-ROM data, then the user must switch scrambling off in the CDR60. These 2 bits select the input format to the encoder; see Table 93. normal input data to encoder all zero input data to encoder random input data to encoder 46 Preliminary specification ScramOn InputFmt.1 DESCRIPTION INPUT FORMAT SAA7392 InputFmt.0 ...

Page 47

... S0 and S1 bytes are generated by the SAA7392. The Q-channel CRC is calculated from the SRI data Q-bits and hence the 16 Q-channel CRC bits in the SRI data are discarded. Auto-format mode. In this mode, the SAA7392 will generate subcode data itself. However, only P and Q subcode channels are supported. 7.12.1 ...

Page 48

... X All other settings are reserved. 48 Preliminary specification copy_alter zero_inc DESCRIPTION Q-CHANNEL TIME FIELD SAA7392 0 time3 ...

Page 49

... QCD.7 QCD.6 2000 Mar EGISTER UB ONFIG 5 4 relcnt.2 relcnt.1 relcnt EGISTER UB TART ATA ATA 5 4 QCD.5 QCD.4 QCD.3 49 Preliminary specification curcnt.2 curcnt.1 DESCRIPTION DESCRIPTION QCD.2 QCD.1 SAA7392 0 curcnt QCD.0 ...

Page 50

... It does this based on the QSync signal it receives from the subcode insert block and the ATIPSync and W441 disc position information it receives from the Wobble processor EGISTER NCODE Count.4 Count.3 DESCRIPTION 50 Preliminary specification SAA7392 2 1 Count.2 Count.1 Count.0 0 ...

Page 51

... W441 when stopping the encode process NCODE FFSET 5 4 XOffset.5 XOffset.4 XOffset.3 XOffset.9 Offset applied to the phase error calculated between ATIPSync and Q-code sync. 51 Preliminary specification ) DESCRIPTION DESCRIPTION XOffset.2 XOffset.1 XOffset.8 XOffset.7 DESCRIPTION SAA7392 XOffset.0 XOffset.6 ...

Page 52

... The EFM modulator This block takes data from the data encoder block and adds the subcode and synchronisation information. This data stream is modulated using EFM according to the Red Book standard. This data is output serially from the SAA7392, with the associated EFM clock signal. ...

Page 53

... X X 2000 Mar (EFMM C EGISTER OD ONFIG DESCRIPTION 0 hold data output at zero 1 output normal data 0 output I3 pattern 1 output I11 pattern 1 output special OPC pattern 3-3-4-4-5-5-6-6-7-7 X All other settings are reserved. 53 Preliminary specification 2 TIM2Mode TIM2ClkOn OUTPUT DATA FORMAT SAA7392 0 DataSel.2 ...

Page 54

... Finally, a programmable divider is used to enable the clock output, XEFM doubled producing XEFM_2. handbook, full pagewidth W441 WCLK MUX Sysclk/192 XError MUX Fifo filling Sysclk Config Data 2000 Mar 21 DIGITAL ANALOG MUX PLL PLL INTEGRATOR Fig.18 EFM PLL block diagram. 54 Preliminary specification SAA7392 PROGRAMMABLE XEFM DIVIDER MGR808 ...

Page 55

... Analog PLL output is divided by 3 (XEFM_2 output is not available). 1 Analog PLL output is divided Analog PLL output is divided Analog PLL output is divided Analog PLL output is divided by 12. 1 Analog PLL output is divided by 16. 55 Preliminary specification Div.1 Div.0 PLL BANDWIDTH PLL DIVISOR SAA7392 0 ...

Page 56

... R 2 (EFMC C EGISTER LOCK ONF 5 4 PosSrc.1 PosSrc.0 DPLLMF.3 FREQUENCY SOURCE 2 S/EBU input. POSITION SOURCE DPLLMF 294 0 1 196 1 0 147 73 36.75 56 Preliminary specification DPLLMF.2 DPLLMF.1 DESCRIPTION DIGITAL PLL MULTIPLICATION FACTOR SAA7392 0 DPLLMF.0 ...

Page 57

... Mar (EFMC C EGISTER LOCK ONF IntegVal.4 IntegVal.3 Kp.1 Kp.0 Ki 0.5 0 0.25 i Ki 0.125 0 1 0.0625 1 1 0.03125 0 1 0.015625 1 1 0.0078125 57 Preliminary specification IntegVal.2 IntegVal.1 Ki.2 Ki.1 COEFFICIENT K p COEFFICIENT K i SAA7392 0 IntegVal.0 Ki.0 ...

Page 58

... PosErr.3 392 196 98 49 ANALOG PLL MULTIPLICATION FACTOR 294 4 147 Preliminary specification 1 / EFM frames and Samplerate.1 Samplerate.0 PosErr.2 PosErr.1 SAMPLE RATE PROGRAMMABLE DIVIDER FACTOR SAA7392 0 PosErr.0 POSITION ERROR TIME CONSTANT 2581 ms 635 ms 160 ms ...

Page 59

... Loop bandwidth should be approximately equal to bit rate to get good detector performance Loop bandwidth depends on ATIP signal scaling. Current figures are valid for 6 dB scaling PLL lock-in range is approximately equal to loop bandwidth. 59 Preliminary specification T ATIP HE BIT DETECTOR T ATIP HE READ INTERFACE LoopBW.2 LoopBW.1 WindWidth.2 WindWidth.1 WindWidth.0 DESCRIPTION SAA7392 0 LoopBW.0 ...

Page 60

... MHz system clock 0 2.65 kHz for 4.26 MHz system clock 1 1.32 kHz for 4.26 MHz system clock 0 662 Hz for 4.26 MHz system clock 1 331 Hz for 4.26 MHz system clock 0 166 Hz for 4.26 MHz system clock for 4.26 MHz system clock DESCRIPTION 60 Preliminary specification SAA7392 LOOP BANDWIDTH ...

Page 61

... MHz system clock 0 10.7 kHz for 4.26 MHz system clock 1 5.4 kHz for 4.26 MHz system clock 0 2.7 kHz for 4.26 MHz system clock 1 1.35 kHz for 4.26 MHz system clock 0 670 Hz for 4.26 MHz system clock 1 350 Hz for 4.26 MHz system clock 61 Preliminary specification PLLHBW.2 PLLHBW.1 DESCRIPTION SAA7392 0 PLLHBW.0 ...

Page 62

... These 8 bits form the most significant byte of the PLL frequency OBBLE REQ 5 4 PLLFreq.4 PLLFreq.3 These 8 bits form the least significant byte of the PLL frequency. 62 Preliminary specification SyncErr DESCRIPTION PLLFreq.10 PLLFreq.9 DESCRIPTION PLLFreq.2 PLLFreq.1 DESCRIPTION SAA7392 0 OIS 0 PLLFreq.8 0 PLLFreq.0 ...

Page 63

... ATIPData.3 least significant byte of ATIP data ( EGISTER OBBLE TATUS 5 4 WPPV.5 WPPV.4 WPPV ATER.5 ATER.4 ATER.3 63 Preliminary specification ATIPData.9 DESCRIPTION ATIPData.2 ATIPData.1 DESCRIPTION WPPV.2 WPPV.1 DESCRIPTION ATER.2 ATER.1 SAA7392 0 ATIPData.8 0 ATIPData.0 0 WPPV.0 0 ATER.0 ...

Page 64

... Equivalent to discharging a 100 pF capacitor via a 1.5 k series resistor with a rise time of 15 ns. 5. Equivalent to discharging a 200 pF capacitor via a 0.75 H series inductor. 2000 Mar 21 CONDITIONS notes 1 and 2 notes 1 and 2 notes 1 and 2 note 4 note 5 ) and analog and digital core/pad ring supply connections (V DDE 64 Preliminary specification SAA7392 MIN. MAX. UNIT 0.5 +4.0 V 0.5 +4.0 V 0.5 +4.0 V ...

Page 65

... DD MOTO2/T3 65 Preliminary specification MIN. TYP. MAX. 3.0 3.3 3.6 3.0 3.3 3.6 3.0 3.3 3.6 200 0.3V 0. PCA , DATAI, SUB, SFSY 0.8 2.0 5.0 10 +10 10 0.4 0.85V 0.4 0.85V +10 0.3V 0.7V 5.0 DD SAA7392 UNIT AND ...

Page 66

... 0. 100 kHz Preliminary specification SAA7392 TYP. MAX. UNIT + 0 0. 5 250 ns 0. ...

Page 67

... MS/s; 1 MHz input top ladder reference provided externally 0.5 effective bits) defines sample rate for 6.5-bit accuracy 17.5 MHz COMMENTS 3 dB point in bandwidth of 35 MHz in bandwidth of 35 MHz f = 17.5 MHz 1.44 V; ADC load out(p-p) peak-to-peak value nominal, at HIN 67 Preliminary specification SAA7392 ...

Page 68

... At this point the encoder starts reading data from the serial interface but stops again after a few milliseconds because the its FIFO gets filled as the data out to the EFM modulator is still blocked. 68 Preliminary specification SAA7392 2 S bit clock and FIFO filling ...

Page 69

... When an audio stream is input to the CDR60 encoder the EFM clock must lock to the serial input WCLK clock signal. The position error is taken from the FIFOFill signal. This will produce an EFM clock that is 98 times the WCLK frequency. 69 Preliminary specification SAA7392 ...

Page 70

... scale (1) ( 0.27 0.18 12.1 12.1 14.15 14.15 0.5 0.13 0.12 11.9 11.9 13.85 13.85 REFERENCES JEDEC EIAJ MS-026 70 Preliminary specification detail 0.75 1.0 0.2 0.15 0.1 0.30 EUROPEAN PROJECTION SAA7392 SOT315 (1) ( 1.45 1. 1.05 1.05 0 ISSUE DATE 99-12-27 00-01-19 ...

Page 71

... Use a low voltage ( less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds 300 C. When using a dedicated tool, all other leads can be soldered in one operation within seconds between 270 and 320 C. 71 Preliminary specification SAA7392 ...

Page 72

... Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm. 2000 Mar 21 SOLDERING METHOD WAVE not suitable (2) not suitable suitable (3)(4) not recommended (5) not recommended 72 Preliminary specification SAA7392 (1) REFLOW suitable suitable suitable suitable suitable ...

Page 73

... Philips. This specification can be ordered using the code 9398 393 40011. 2000 Mar 21 C COMPONENTS 2 C components conveys a license under the Philips’ system provided the system conforms to the I 73 Preliminary specification SAA7392 2 C patent to use the 2 C specification defined by ...

Page 74

... Philips Semiconductors Channel encoder/decoder CDR60 2000 Mar 21 NOTES 74 Preliminary specification SAA7392 ...

Page 75

... Philips Semiconductors Channel encoder/decoder CDR60 2000 Mar 21 NOTES 75 Preliminary specification SAA7392 ...

Page 76

Philips Semiconductors – a worldwide company Argentina: see South America Australia: 3 Figtree Drive, HOMEBUSH, NSW 2140, Tel. +61 2 9704 8141, Fax. +61 2 9704 8139 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. + 101 ...