lm4550 National Semiconductor Corporation, lm4550 Datasheet - Page 11

lm4550

Manufacturer Part Number

lm4550

Description

Ac ?97 Rev 2.1 Multi-channel Audio Codec With Stereo Headphone Amplifier, Sample Rate Conversion And National 3d Sound

Manufacturer

National Semiconductor Corporation

Datasheet

1.LM4550.pdf

(25 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

lm4550BVH/NOPB

Manufacturer:

STM

Quantity:

1 872

Company:

Part Number:

lm4550BVH/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

Company:

Part Number:

lm4550BVHX

Manufacturer:

Texas Instruments

Quantity:

10 000

Company:

Part Number:

lm4550BVHX/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

Company:

Part Number:

lm4550VH/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

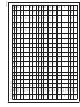

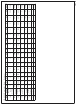

SDATA_OUT

Pin Descriptions

SDATA_IN

VREFOUT

CHAIN_IN

XTL_OUT

BIT_CLK

RESET#

XTL_IN

AFILT1

DVDD

Name

SYNC

EAPD

Name

AVDD

DVSS

VREF

AVSS

ID0

ID1

Pin

Pin

1,9

4,7

10

11

45

46

47

48

25

26

27

28

29

2

3

5

6

8

I / O

I / O

I/O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

(Continued)

24.576 MHz crystal input. Use a fundamental-mode type crystal. When operating from a

crystal, a 1MΩ resistor must be connected across pins 2 and 3.

24.576 MHz crystal output. When operating from a crystal, a 1MΩ resistor must be connected

across pins 2 and 3.

This data stream contains both control data and DAC audio data. This input is sampled by

the LM4550 on the falling edge of BIT_CLK.

OUTPUT when in Primary Codec Mode: This pin outputs a 12.288 MHz clock which is

derived (internally divided by two) from the 24.576MHz crystal input (XTL_IN).

INPUT when in Secondary Codec Mode (Multiple Codec configurations only): 12.288MHz

clock is to be supplied from an external source, such as from the BIT_CLK of a Primary

Codec.

This data stream contains both control data and ADC audio data. This output is clocked out

by the LM4550 on the rising edge of BIT_CLK.

48kHz sync pulse which signifies the beginning of both the SDATA_IN and SDATA_OUT

serial streams. SYNC must be synchronous to BIT_CLK.

This active low signal causes a hardware reset which returns the control registers to their

default conditions.

ID0 and ID1 set the codec address for multiple codec use where ID0 is the LSB. Connect

these pins to DVdd or GND as required. If these pins are not connected (NC), they default to

Primary codec setting (same as connecting both pins to DVdd). These pins are of inverted

polarity relative to their internal ID0, ID1 registers. If pin 45 is connected to GND, then ID0 will

be set to "1" internally. Connection to DVdd corresponds to a "0" internally.

ID0 and ID1 set the codec address for multiple codec use where ID1 is the MSB. Connect

these pins to DVdd or GND as required. If these pins are not connected (NC), they default to

Primary codec setting (same as connecting both pins to DVdd). These pins are of inverted

polarity relative to their internal ID0, ID1 registers. If pin46 is connected to GND, then ID1 will

be set to "1" internally. Connection to DVdd corresponds to a "0" internally.

The contents of "Powerdown Ctrl/Stat" register 26h bit 15 determines the logic level output on

this pin. This pin is to be connected to an external power amplifier’s shutdown pin. The output

voltage is set by the digital supply. If EAPD=0, then a logic low is output and the external

amplifer is enabled. If EAPD=1, the amplifer is shutdown. Power up default is EAPD=0.

By setting the two LSBs of register 74h to something other than the codec ID, the codec

stops sending its own SDATA_IN signal and instead passes the signal connected here out the

SDATA_IN pin. This pin can be left floating if no software will use register 74h and the chain

feature is not used. When the chain feature is used, another codec’s SDATA_IN pin should

be connected here, or else this pin should be grounded to prevent the possibility of floating

the SDATA_IN signal at the controller.

Analog supply.

Analog ground.

Digital supply.

Digital ground.

Nominal 2.2V reference output. Not intended to sink or source current. Bypassing of this pin

should be done with short traces to maximize performance.

Nominal 2.2V reference output. Can source up to 5mA of current and can be used to bias a

microphone.

This pin is not used and should be left open (NC). However, a capacitor to ground on this pin

is permitted - it will not affect performance.

POWER SUPPLIES AND REFERENCES

DIGITAL I/O AND CLOCKING

11

Functional Description

Functional Description

www.national.com