ocx256 ETC-unknow, ocx256 Datasheet - Page 17

ocx256

Manufacturer Part Number

ocx256

Description

Ocx256 Crosspoint Switch

Manufacturer

ETC-unknow

Datasheet

1.OCX256.pdf

(47 pages)

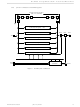

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

I [3:0]

1.4.8

Fairchild Semiconductor

BB

X

X

X

X

X

X

X

X

JTAG Instructions

Clock

Select

BA

X

X

X

X

X

X

X

Mode

Data

B9

X

X

X

X

X

X

X

OE

B8

X

X

X

X

X

X

X

OE

B7

X

X

X

X

X

X

X

Table 8

Output Address/

Output Buffer

Address

OCX256 Crosspoint Switch—Advanced Datasheet

A6-A0

Buffer

[Rev. 2.0] 3/21/02

X

X

X

X

X

X

JTAG Instructions

Sample/EXTEST

Sample/EXTEST

Reset the Crosspoint

Array

Set Array for

Broadcast mode

Program a Buffer

Configuration

readback

Update the

Crosspoint Array

Disconnect Input

cell

Instruction

Places the device in scan mode.

Places the device in scan mode.

Resets the entire Crosspoint Array to no-connect. All

other Output Buffer configurations are unchanged by

this operation.

Use the JTAG Address Register as the Input address to

be the broadcast input Connects the selected Input to

all Output cells and disconnects all other Inputs.

Activating the Global Update JTAG instruction returns

the Crosspoint array from the Broadcast mode to the

previous programed state.

Programs the Output Buffer address specified in the

JTAG instruction (A6-A0). The configuration data is

also specified in the JTAG instruction bits BA-B7. See

Table 9 for bit assignment of the Buffer functionality.

Readback the connectivity of the Crosspoint cell with

the Input location specified in the JTAG Address

Register and the Output location specified JTAG

instruction (A0-A6). It also returns the configuration of

the Output Buffer addressed in the JTAG instruction

(A0-A6).

The readback data is shifted out of TDO in the

following sequence:

NOTE: This instruction does not increment the JTAG

Address Register. This instruction also requires two

DR cycles

Update the programmed connection from the Loading

SRAM to the Active SRAM.

Disconnect the Crosspoint connections from the Input

address specified in the JTAG Address Register.

1. Crosspoint Connect (1=connected, 0=no

2. Output Enable—B7 (see Table 9)

3. Output Enable—B8 (see Table 9)

4. Output Data Source—B9 (0=Flow-through,

5. Output Clock Select—BA (0=Global Clock,

6. State of Broadcast bit

7. State of the RCE bit

connection)

1=registered)

1=Next Neighbor)

Description

17