HCS160DMSR INTERSIL [Intersil Corporation], HCS160DMSR Datasheet

HCS160DMSR

Related parts for HCS160DMSR

HCS160DMSR Summary of contents

Page 1

... CMOS/SOS Logic Family. The HCS160MS is supplied lead Ceramic flatpack (K suffi SBDIP Package (D suffix.) Ordering Information PART NUMBER TEMPERATURE RANGE HCS160DMSR HCS160KMSR HCS160D/Sample HCS160K/Sample HCS160HMSR CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. ...

Page 2

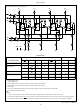

Functional Block Diagram P0 3 SPE GND VCC OPERATING MODE MR Reset (Clear) L Parallel Load H H Count H Inhibit ...

Page 3

Absolute Maximum Ratings Supply Voltage (VCC -0.5V to +7.0V Input Voltage Range, All Inputs . . ...

Page 4

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS PARAMETER SYMBOL TPHL, VCC = 4.5V TPLH TPHL, VCC = 4.5V TPLH TPHL, VCC = 4.5V TPLH TPHL VCC ...

Page 5

TABLE 4. DC POST RADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued) PARAMETER SYMBOL Output Current IOH VCC = 4.5V, VIN = VCC or GND, (Source) VOUT = VCC -0.4V Output Voltage Low VOL VCC = 4.5V and 5.5V, VIH = 0.70(VCC), VIL ...

Page 6

CONFORMANCE GROUPS Initial Test (Preburn-In) Interim Test I (Postburn-In) Interim Test II (Postburn-In) PDA Interim Test III (Postburn-In) PDA Final Test Group A (Note 1) Group B Subgroup B-5 Subgroup B-6 Group D NOTE: 1. Alternate Group A testing in ...

Page 7

Intersil Space Level Product Flow - ‘MS’ Wafer Lot Acceptance (All Lots) Method 5007 (Includes SEM) GAMMA Radiation Verification (Each Wafer) Method 1019, 4 Samples/Wafer, 0 Rejects 100% Nondestructive Bond Pull, Method 2023 Sample - Wire Bond Pull Monitor, Method ...

Page 8

AC Timing Diagrams VIH INPUT VS VIL TPLH VOH VS OUTPUT VOL TTLH VOH 80% 20% OUTPUT VOL AC VOLTAGE LEVELS PARAMETER HCS VCC 4.50 VIH 4.50 VS 2.25 VIL 0 GND 0 HCS160MS AC Load Circuit TPHL TTHL 80% ...

Page 9

Die Characteristics DIE DIMENSIONS: 104 x 86 mils METALLIZATION: Type: AlSi Å Å Metal Thickness: 11k 1k GLASSIVATION: Type: SiO 2 Å Å Thickness: 13k 2.6k WORST CASE CURRENT DENSITY <2 A/cm BOND PAD SIZE: 100 ...