CDP1854 Intersil Corporation, CDP1854 Datasheet

CDP1854

Available stocks

Related parts for CDP1854

CDP1854 Summary of contents

Page 1

... The CDP1854A and the CDP1854AC are functionally identi- 10V/400K PKG. cal. The CDP1854A has a recommended operating voltage BAUD NO. range 10.5V, and the CDP1854AC has a recom- CDP1854AE E40.6 mended operating voltage range 6.5V. E40.6 CDP1854AQ N44.65 CDP1854AD D40 ...

Page 2

... R CLOCK 17 DAR SDI 20 R BUS 6 R BUS 5 R BUS 4 R BUS 3 R BUS BUS 1 R BUS 0 PE(INT) FE OE(PE/OE) NOTE: MODE 0(MODE 1) CDP1854A, CDP1854AC 40 LEAD SBDIP, PDIP (MODE CLOCK EPE MODE ( WLS WLS 2 CS2 36 SBS R BUS ...

Page 3

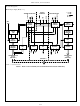

... TRANSMITTER 25 PARITY GEN TRANSMITTER SHIFT REGISTER TRANSMITTER CONTROL HOLDING REG REGISTER TRANSMITTER BUS (26 - 33) (SEE NOTE 1) NOTE: 1. User Interconnect FIGURE 1. MODE 1 BLOCK DIAGRAM (CDP1800-SERIES MICROPROCESSOR COMPATIBLE) CDP1854A, CDP1854AC CDP1802 INTERFACE TIMING & CONTROL SELECT INT LOGIC (SEE NOTE 1) ...

Page 4

... Absolute Maximum Ratings DC Supply-Voltage Range (Voltages Referenced to V Terminal) SS CDP1854A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +11V CDP1854AC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +7V Input Voltage Range, All Inputs . . . . . . . . . . . . . .-0 Input Current, Any One Input Device Dissipation Per Output Transistor T = Full Package-Temperature Range . . . . . . . . . . . . . . 100mW A Operating-Temperature Range ( Package Type -55 Package Type E and -40 CAUTION: Stresses above those listed in “ ...

Page 5

... Operating Conditions Full Package-Temperature Range. For maximum reliability, operating conditions should be selected so A that operation is always within the following ranges: PARAMETER DC Operating Voltage Range Input Voltage Range Baud Rate (Receive or Transmit) CDP1854A, CDP1854AC - +85 C, Unless Otherwise Noted (Continued) A CDP1854A V ...

Page 6

... Functional Definitions for CDP1854A Terminals Mode 1 CDP1800-Series Microprocessor Compatible SIGNAL: FUNCTION Positive supply voltage. MODE SELECT (MODE): A high-level voltage at this input selects CDP1800-series microprocessor Mode operation Ground CHIP SELECT 2 (CS2): A low-level voltage at this input together with CS1 and CS3 selects the CDP1854A UART ...

Page 7

... Transmitter Shift Register and may be reloaded with a new character. Setting this bit also sets the THRE output (Term. 22) low and causes an INTERRUPT (lNT = low high. CDP1854A, CDP1854AC TRANSMITTER CLOCK (TCLOCK): Clock input with a frequency 16 times the desired transmitter shift rate ...

Page 8

... The receiver and transmitter buses are connected to the bus. CDP1800-series microprocessor I/O control output signals can be connected directly to the CDP1854A inputs as shown in Figure 2. The CLEAR input is pulsed, resetting the Control, Status, and Receiver Holding Registers and setting SERIAL DATA OUT (SDO) high. The Control Register is loaded from the Transmitter Bus in order to determine the operating confi ...

Page 9

... CDP1854A, CDP1854AC the microprocessor and resets DATA AVAILABLE (DA) in the UART. The preceding sequence is repeated for each serial character which is received from the peripheral. Peripheral Interface In addition to serial data in and out, four signals are provided for communication with a peripheral. The REQUEST TO SEND (RTS) output signal alerts the peripheral to get ready to receive data ...

Page 10

... The Transmitter Shift Register is loaded on the first high-to-low transition of the clock which occurs at least 1/2 clock period + t the trailing edge of TPB and transmission of a start bit occurs 1/2 clock period + t 3. Write is the overlap of TPB, CS1, and CS3 = 1 and CS3, RD/ FIGURE 3. TRANSMITTER TIMING DIAGRAM - MODE 1 CDP1854A, CDP1854AC ...

Page 11

... Clock to DATA AVAILABLE Clock to Overrun Error Clock to Parity Error Clock to Framing Error NOTES Typical values for and nominal voltages Maximum limits of minimum characteristics are the values above which all devices function. CDP1854A, CDP1854AC - + 5 20ns ...

Page 12

... OE and PE share terminal 15 and are also available as two separate bits in the status register. TPB (NOTE 1) RSEL T BUS 0- T BUS 7 CS3, CS1 (NOTE 1) RD/WR, CS2 (NOTE 1) NOTE: 1. Write is the overlap of TPB, CS1, CS3 = 1 and CS2, RD/ FIGURE 5. MODE 1 CPU INTERFACE (WRITE) TIMING DIAGRAM CDP1854A, CDP1854AC CLOCK 7 1/2 SAMPLE START BIT PARITY ...

Page 13

... RESEL to Data Valid Time t RSDV Hold Time Data after Read t RDH NOTES Typical values for and nominal voltages Maximum limits of minimum characteristics are the values above which all devices function. CDP1854A, CDP1854AC - + 5 20ns ...

Page 14

... PARITY GEN TRANSMITTER SHIFT 25 REGISTER TRANSMITTER HOLDING REGISTER THRL TRANSMITTER BUS TRANSMITTER SECTION FIGURE 7. MODE 0 BLOCK DIAGRAM (INDUSTRY STANDARD COMPATIBLE) CDP1854A, CDP1854AC t RST t RSDV t RDDA t RDV T CLOCK R CLOCK 40 17 RECEIVER TIMING AND TIMING AND ...

Page 15

... Functional Definitions for CDP1854A Terminals Standard Mode 0 SIGNAL: FUNCTION Positive supply voltage. MODE SELECT (MODE): A low-level voltage at this input selects Standard Mode 0 Operation Ground. RECEIVER REGISTER DISCONNECT (RRD): A high-level voltage applied to this input disconnects the Receiver Holding Register from the Receiver Bus. ...

Page 16

... RECEIVER BUS (R BUS BUS 7) out- puts. Applying a negative pulse to the DATA AVAILABLE RESET (DAR) resets DA. The preceding sequence of opera- tion is repeated for each serial character received. A receiver timing diagram is shown in Figure 11 5-57 . The CDP1854A is then ready for DD ...

Page 17

... CONTROL INPUT WORD TIMING CONTROL WORD INPUT CRL STATUS OUTPUT TIMING STATUS OUTPUTS t SFDH SFD RECEIVER REGISTER DISCONNECT TIMING R BUS 0 R BUS 7 t RRDH RRD FIGURE 9. MODE 0 INTERFACE TIMING DIAGRAM CDP1854A, CDP1854AC - + 5 20ns (See Figure 9) ...

Page 18

... Clock to Data Start Bit Clock to THRE THRL to THRE Clock to TSRE NOTES Typical values for and nominal voltages Maximum limits of minimum characteristics are the values above which all devices function. CDP1854A, CDP1854AC - + 5 20ns ...

Page 19

... Clock to Data Available Clock to Overrun Error Clock to Parity Error Clock to Framing Error NOTES Typical values for and nominal voltages Maximum limits of minimum characteristics are the values above which all devices function. CDP1854A, CDP1854AC - + 5 20ns ...

Page 20

... If a pending DA has not been cleared by a read of the receiver holding register by the time a new word is loaded into the receiver holding register, the OE signal will come true. FIGURE 11. MODE 0 RECEIVER TIMING DIAGRAM START BIT CDP1854A, CDP1854AC TRANSMITTER HOLDING REGISTER LOADED (NOTE 1) ...

Page 21

... For information regarding Intersil Corporation and its products, see web site http://www.intersil.com Sales Office Headquarters NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240 CDP1854A, CDP1854AC EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ...