CXA3572 Sony Corporation, CXA3572 Datasheet - Page 25

CXA3572

Manufacturer Part Number

CXA3572

Description

Driver/Timing Generator for Color LCD Panels

Manufacturer

Sony Corporation

Datasheet

1.CXA3572.pdf

(40 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CXA3572AR

Manufacturer:

TEMIC

Quantity:

50 000

Part Number:

CXA3572AR

Manufacturer:

SONY/索尼

Quantity:

20 000

Company:

Part Number:

CXA3572R-T4

Manufacturer:

DSP

Quantity:

154

Part Number:

CXA3572R-T4

Manufacturer:

SONY/索尼

Quantity:

20 000

2) Common voltage generation circuit block

The common voltage circuit generates and supplies the common pad voltage to the LCD panel. The voltage is

offset by serial communication using the SIG.C voltage as the reference and then output.

3) DA OUT output circuit

The DA OUT output circuit outputs DC 3.0V at equal divisions.

4) REF output circuit

The REF output circuit generates and supplies the panel level shifter circuit reference voltage to the LCD

panel.

5) Sync system

• Internal sync separation circuit

• PLL and AFC circuits (VCO setting method)

6) Power saving circuit (PS circuit)

A power saving system can be realized together with the LCD panel by independently controlling (serial

communication) the operation of each output block. This system is also effective for improving picture quality

during power-on/off.

Sync separation is performed from the signal input from SYNC IN (Pin 25). An external sync signal can also

be input from the same pin (SYNC IN) according to the serial communication setting.

A PLL circuit can be comprised by connecting a PLL circuit phase comparator and frequency division

counter and a VCO circuit and external LPF circuit. The PLL error detection signal is generated using the

phase comparison output of the entire bottom of the horizontal sync signal and the internal frequency

division counter as the RPD output. RPD output is converted to DC error voltage with the lag-lead filter, and

then it controls the internal VCO circuit to stabilize the oscillation frequency.

The internal clock oscillation frequency is set as follows by adjusting VCO-Coarse/Fine.

Adjust the VCO-Coarse/Fine settings so that the HDO pulse output frequency in the condition without sync

input is NTSC: 15.734 ± 0.1kHz and PAL: 15.625 ± 0.1kHz.

The serial data PS0 and SYNC GEN must be set in order to use this IC.

For details of the setting methods, see the “Description of Serial Control Operation” and “Power supply

and power saving sequence” items.

Serial communication setting

Input pin (Pin 25) processing

Clock oscillation

frequency

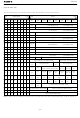

VCO-Coarse: f0 coarse setting (7 steps) from 5 to 25MHz

VCO-Fine: Variable by approximately 4MHz using the f0 coarse setting made by

SYNC SEL = 0: Internal sync separation.

SYNC SEL = 1: External sync signal input. (The internal sync separation circuit is set to power

During internal sync separation: Input through an external capacitor (0.1µF)

During external sync signal input: Directly coupled, input level 3Vp-p positive or negative polarity

VCO-Coarse as the reference

5MHz

saving mode.)

– 25 –

Min: 25MHz

Max: 30MHz

VCO-Fine setting range (255 steps)

VCO-Coarse setting

(7 steps)

CXA3572R