LCMXO2-1200ZE-1TG100C Lattice, LCMXO2-1200ZE-1TG100C Datasheet - Page 77

LCMXO2-1200ZE-1TG100C

Manufacturer Part Number

LCMXO2-1200ZE-1TG100C

Description

FPGA - Field Programmable Gate Array 1280 LUTs 80 I/O 1.2V -1 SPD

Manufacturer

Lattice

Datasheet

1.LCMXO2-256HC-4SG32I.pdf

(106 pages)

Specifications of LCMXO2-1200ZE-1TG100C

Rohs

yes

Number Of I/os

80

Maximum Operating Frequency

104 MHz

Operating Supply Voltage

1.2 V

Maximum Operating Temperature

+ 100 C

Mounting Style

SMD/SMT

Package / Case

TQFP-100

Minimum Operating Temperature

+ 85 C

Operating Supply Current

58 uA

Factory Pack Quantity

90

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LCMXO2-1200ZE-1TG100C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LCMXO2-1200ZE-1TG100CR1

Manufacturer:

Lattice

Quantity:

87

Company:

Part Number:

LCMXO2-1200ZE-1TG100CR1

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

January 3013

Signal Descriptions

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

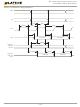

General Purpose

P[Edge] [Row/Column

Number]_[A/B/C/D]

NC

GND

VCC

VCCIOx

PLL and Clock Functions (Used as user-programmable I/O pins when not used for PLL or clock pins)

[LOC]_GPLL[T, C]_IN

[LOC]_GPLL[T, C]_FB

PCLK [n]_[2:0]

Test and Programming (Dual function pins used for test access port and during sysCONFIG™)

TMS

TCK

TDI

TDO

JTAGENB

Configuration (Dual function pins used during sysCONFIG)

PROGRAMN

INITN

Signal Name

I/O

I/O

I/O

—

—

—

—

—

—

—

O

I

I

I

I

I

[Edge] indicates the edge of the device on which the pad is located. Valid edge designations

are L (Left), B (Bottom), R (Right), T (Top).

[Row/Column Number] indicates the PFU row or the column of the device on which the PIO

Group exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When

Edge is L (Left) or R (Right), only need to specify Column Number.

[A/B/C/D] indicates the PIO within the group to which the pad is connected.

Some of these user-programmable pins are shared with special function pins. When not used

as special function pins, these pins can be programmed as I/Os for user logic.

During configuration of the user-programmable I/Os, the user has an option to tri-state the

I/Os and enable an internal pull-up, pull-down or buskeeper resistor. This option also applies

to unused pins (or those not bonded to a package pin). The default during configuration is for

user-programmable I/Os to be tri-stated with an internal pull-down resistor enabled. When the

device is erased, I/Os will be tri-stated with an internal pull-down resistor enabled. Some pins,

such as PROGRAMN and JTAG pins, default to tri-stated I/Os with pull-up resistors enabled

when the device is erased.

No connect.

GND – Ground. Dedicated pins. It is recommended that all GNDs are tied together.

V

are tied to the same supply.

VCCIO – The power supply pins for I/O Bank x. Dedicated pins. It is recommended that all

VCCIOs located in the same bank are tied to the same supply.

Reference Clock (PLL) input pads: [LOC] indicates location. Valid designations are L (Left

PLL) and R (Right PLL). T = true and C = complement.

Optional Feedback (PLL) input pads: [LOC] indicates location. Valid designations are L (Left

PLL) and R (Right PLL). T = true and C = complement.

Primary Clock pads. One to three clock pads per side.

Test Mode Select input pin, used to control the 1149.1 state machine.

Test Clock input pin, used to clock the 1149.1 state machine.

Test Data input pin, used to load data into the device using an 1149.1 state machine.

Output pin – Test Data output pin used to shift data out of the device using 1149.1.

Optionally controls behavior of TDI, TDO, TMS, TCK. If the device is configured to use the

JTAG pins (TDI, TDO, TMS, TCK) as general purpose I/O, then:

If JTAGENB is low: TDI, TDO, TMS and TCK can function a general purpose I/O.

If JTAGENB is high: TDI, TDO, TMS and TCK function as JTAG pins.

For more details, refer to TN1204,

Initiates configuration sequence when asserted low. This pin always has an active pull-up.

Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up

is enabled.

CC

– The power supply pins for core logic. Dedicated pins. It is recommended that all VCCs

MachXO2 Family Data Sheet

4-1

MachXO2 Programming and Configuration Usage

Descriptions

Pinout Information

DS1035

Pinout Information_01.7

Data Sheet DS1035

Guide.