LP3927ILQ-AZ/NOPB National Semiconductor, LP3927ILQ-AZ/NOPB Datasheet - Page 15

LP3927ILQ-AZ/NOPB

Manufacturer Part Number

LP3927ILQ-AZ/NOPB

Description

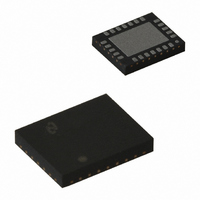

IC PWR MNGMNT CELL/PCS 28-LLP

Manufacturer

National Semiconductor

Datasheet

1.LP3927ILQX-AP.pdf

(17 pages)

Specifications of LP3927ILQ-AZ/NOPB

Applications

Handheld/Mobile Devices

Current - Supply

5µA

Voltage - Supply

3 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

28-LLP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

LP3927ILQ-AZ

Application Hints

LP3927 FUNCTION DESCRIPTION

The LP3927 is designed for cellular/PCS handsets. The

LDOs power the microprocessor, RF and digital sections of

the phone. When a KYBD debounce of longer than 32 ms is

detected by the LP3927, the IRQ signal is asserted and sent

to the microprocessor. In addition, the KYBD signal turns on

LDO1. When LDO1 reaches 95% of its output voltage op-

tion, a 125 µs delay (standard LDO delay. The optional LDO

delay has a 10msec delay) takes place, and LDO2 turns on.

When LDO2 reaches 95% of its output voltage option, RST

goes high after a 20 ms delay. At this point, the micropro-

cessor comes out of reset and the LP3927 starts the PS_H-

OLD timer. If PS_HOLD goes high before 500 ms, IRQ is

de-asserted. If PS_HOLD stays low for longer than 500 ms,

IRQ will still de-assert, but RST will also be asserted, and the

part will power down.

The power down sequence is the exact reverse of the power

up sequence. PS_HOLD from the microprocessor goes low,

indicating a request to turn the part off. This causes RST to

go low. LDO2 will be turned off after a 20 ms delay. When

LDO2 drops to 90% of its output voltage option, LDO1 will

start to turn off after a 125 µs (or a 10msec) delay. Another

KYBD debounce after power up does not necessary mean

power down.

Whenever LDO1 or LDO2 falls under 90% of the output

voltage option, RST immediately goes low to bring

PS_HOLD low in order to turn the part off.

Plugging the charger into the cell phone will cause an exter-

nal signal VEXT to toggle from high to low. The LP3927 will

respond differently to this signal depending on the scenario:

Case 1: If a charger is plugged into the cell phone after the

phone is already on, the VEXT signal go from high to low.

The LP3927 will acknowledge this signal but all other signals

remain unchanged.

Case 2: If a charger is plugged into the phone while the

phone is off, VEXT signal goes from high to low and the

LP3927 will proceed to turn LDO1 on after a 32 ms delay,

and the identical power-up sequence follows. This case

bypasses the power-up initiated by KYBD and IRQ. KYBD

remains low and IRQ remains high at all time during power-

up.

When the charger is plugged in, the phone cannot be turned

off unless both VEXT goes high and PS_HOLD goes low.

LDOs

The LP3927 contains five LDOs. LDO1 and 2 are powered

by the V

and LDO5 is powered by the V

must be tied together externally. All five LDOs accept an

input voltage from 3.0V to 5.5V. This accommodates the full

usable range of a single Li-On battery.

LDO1 and 4 each provide 150 mA of current. LDO2 and 5

each provide 200 mA of current. LDO3 provides 100 mA of

current. The output of each LDO can be programmed to

different voltage levels at the factory. Refer to “Output Cur-

rent Rating and Voltage Options” Table for more details.

LDO INPUT CAPACITOR

An input capacitance of ≈ 2.2 µF is required between each

V

may be increased without limit).

DD

input pins and ground. (The amount of the capacitance

DD1

line; LDO3 and 4 are powered by the V

DD3

line. V

DD1

, V

DD2

and V

DD2

line;

DD3

15

This capacitor must be located a distance of not more than

1 cm from the input pin and returned to a clean analog

ground. Any good quality ceramic, tantalum, or film capacitor

may be used at the inputs.

Important: Tantalum capacitors can suffer catastrophic fail-

ures due to surge current when connected to a low-

impedance source of power (like a battery or a very large

capacitor). If a tantalum capacitor is used at the input, it must

be guaranteed by the manufacturer to have a surge current

rating sufficient for the application.

There are no requirements for the ESR on the input capaci-

tor, but tolerance and termperature coefficient must be con-

sidered when selecting the capacitor to ensure the capaci-

tance will be ≈ 1 µF over the entire operating temperature

range.

LDO OUTPUT CAPACITOR

The LDOs are designed specifically to work with very small

ceramic output capacitors. A ceramic capacitor (X7R, X5R,

Z5U, or Y5V) in 1 µF to 20 µF range with 5 mΩ to 500 mΩ

ESR range is suitable in the LP3927 application circuit.

It may also be possible to use tantalum or film capacitors at

the output, but these are not as attractive for reasons of size

and cost.

The output capacitor must meet the requirement for mini-

mum amount of capacitance and also have an ESR (Equiva-

lent Series Resistance) value which is within a stable range

(5 mΩ to 500 mΩ).

LED CURRENT DRIVER

The LED pin on the LP3927 is an open-drain output that can

provide up to 150 mA to drive backlight LEDs. It is turned on

when the LED_EN pin is pulled high, and off when the

LED_EN pin is pulled low. The external resistor R

nected to the LED_PGM pin programs the output current of

LED. A 130 kΩ resistor sets the output current to 150 mA. An

approximated equation between R

OPERATIONAL AMPLIFIER

The LP3927 has an internal op amp with rail-to-rail input and

output and a 600 kHz of gain-bandwidth product.

LEADLESS LEADFRAME PACKAGE (LLP)

The LP3927 is packaged in a 28-lead LLP package for

enhanced thermal performance. The 28-lead LLP measures

5 mm x 5 mm x 0.75 mm. Its small size and low profile is

ideal for handset applications and other portable applications

that require power management.

THERMAL PERFORMANCE

The LLP package is designed for enhanced thermal perfor-

mance because of the exposed die attach pad at the bottom

center of the package. It brings advantage to thermal perfor-

mance by creating a very direct path for thermal dissipation.

Compared to the traditional leaded packages where the die

attach pad is embedded inside the mold compound, the LLP

reduces a layer in the thermal path.

The thermal advantage of the LLP package is fully realized

only when the exposed die attach pad is soldered down to a

thermal land on the PCB board and thermal vias are planted

underneath the thermal land. Based on a LLP thermal mea-

PGM

and I

LED

www.national.com

is:

PGM

con-