ISL6540ACRZ Intersil, ISL6540ACRZ Datasheet - Page 14

ISL6540ACRZ

Manufacturer Part Number

ISL6540ACRZ

Description

IC CTLR PWM BUCK 1PHASE 28-QFN

Manufacturer

Intersil

Datasheet

1.ISL6540ACRZ-T.pdf

(22 pages)

Specifications of ISL6540ACRZ

Pwm Type

Voltage Mode

Number Of Outputs

1

Frequency - Max

2MHz

Duty Cycle

100%

Voltage - Supply

2.97 V ~ 22 V

Buck

Yes

Boost

No

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Frequency-max

2MHz

Number Of Pwm Outputs

1

On/off Pin

No

Adjustable Output

Yes

Topology

Buck

Switching Freq

250 TO 2000kHz

Operating Supply Voltage (max)

5.5V

Output Current

4A

Output Voltage

0.6 to 20V

Synchronous Pin

No

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

28

Package Type

QFN EP

Rohs Compliant

YES

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISL6540ACRZ

Manufacturer:

Intersil

Quantity:

35

Part Number:

ISL6540ACRZ

Manufacturer:

ISL

Quantity:

20 000

internal linear dropout is too large for a given application.

When using the external linear regulator option, the

LIN_DRV pin should be connected to the gate of a PMOS

device, and a resistor should be connected between its gate

and source. A resistor and a capacitor should be connected

from gate-to-source to compensate the control loop. A PNP

device can be used instead of a PMOS device in which case

the LIN_DRV pin should be connected to the base of the

PNP pass element. The sinking capability of the LIN_DRV

pin is 5mA, and should not be exceeded if using an external

resistor for a PMOS device. The designer should take care

in designing a stable system when using external pass

elements. The VCC pin should be connected to the PVCC

pin with an RC filter to prevent high frequency driver

switching noise from entering the analog circuitry.

High Speed MOSFET Gate Driver

The integrated driver has similar drive capability and

features to Intersil's ISL6605 stand alone gate driver. The

PWM tri-state feature helps prevent a negative transient on

the output voltage when the output is being shut down. This

eliminates the Schottky diode that is used in some systems

for protecting the microprocessor from

reversed-output-voltage damage. See the ISL6605

datasheet for specification parameters that are not defined in

the current ISL6540A “Electrical Specifications” table on

page 6.

A 1Ω to 2Ω resistor is recommended to be in series with the

bootstrap diode when using VCCs above 5.0V to prevent the

bootstrap capacitor from overcharging due to the negative

swing of the trailing edge of the phase node.

Margining Control

When the MAR_CTRL is pulled high or low, the positive or

negative margining functionality is respectively enabled.

When MAR_CTRL is left floating, the function is disabled.

Upon UP margining, an internal buffer drives the OFS- pin

from VCC to maintain OFS+ at 0.591V. The resistor divider,

R

increased. Similarly, upon DOWN margining, an internal

buffer drives the OFS+ pin from VCC to maintain OFS- at

0.591V. The resistor divider, R

voltage at OFS+ to be increased. In both modes, the voltage

difference between OFS+ and OFS- is then sensed with an

instrumentation amplifier and is converted to the desired

margining voltage by a 5:1 ratio. The maximum designed

margining range of the ISL6540A is ±200mV, this sets the

MINIMUM value of R

for an R

The OFS pins are completely independent and can be set to

different margining levels. The maximum usable reference

voltage for the ISL6540A is VCC-1.8V, and should not be

exceeded when using the margining functionality, for

MARG

MARG

and R

OFS+

of 10k for a MAXIMUM of 1V across R

, causes the voltage at OFS- to be

OFS+

or R

14

MARG

OFS-

at approximately 5.9k

and R

OFS-

, causes the

MARG

ISL6540A

.

example: V

Equation 8:

An alternative calculation provides for a desired percentage

change in the output voltage when using the internal 0.591V

reference:

When not used in a design OFS+, OFS-, and MARCTRL

should be left floating. To prevent damage to the part, OFS+

and OFS- should not be tied to VCC or PVCC.

Reference Output Buffer

The internal buffer’s output tracks the unmargined system

reference. It has a 19mA drive capability, with maximum and

minimum output voltage capabilities of VCC and GND

respectively. Its capacitive loading can range from 1µF to

above 17.6µF, which is designed for 1 to 8 DIMM systems in

DDR (Dual Data Rate) applications. 1µF of capacitance

should always be present on REFOUT. It is not designed to

drive a resistive load and any such load added to the system

should be kept above 300kΩ total impedance. The

Reference Output Buffer should not be left floating.

Reference Input

The REFIN pin allows the user to bypass the internal 0.591V

reference with an external reference. Asynchronously, if

REFIN is NOT within ~1.8V of VCC, the external reference

pin is used as the control reference instead of the internal

0.591V reference. The minimum usable REFIN voltage is

~68mV, while the maximum is VCC - 1.8V - V

present).

V

V

V

MARG_DOWN

PCT_UP

MARG_UP

REFOUT

REFIN

REFERENCE

V

REF

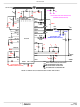

FIGURE 5. SIMPLIFIED REFERENCE BUFFER

=

= 0.591V

REF_MARG

20

=

V

-------------- -

•

=

REF

R

-------------------- -

5

R

V

-------------- -

MARG

OFS+

REF

5

•

R

-------------------- -

R

•

< VCC - 1.8V, as shown in

MARG

OFS+

MARGINING

R

-------------------- -

R

MARG

BLOCK

OFS-

V

pct_DOWN

VCC

800mV

V

REF_MARG

=

20

MARG

•

MACHINE

ISL6540A

R

-------------------- -

R

STATE

October 7, 2008

MARG

OFS-

(if

OTA

FN6288.5

(EQ. 9)

(EQ. 8)