ISL6520ACBZA Intersil, ISL6520ACBZA Datasheet - Page 8

ISL6520ACBZA

Manufacturer Part Number

ISL6520ACBZA

Description

IC CTRLR PWM SYNC BUCK 8-SOIC

Manufacturer

Intersil

Datasheet

1.ISL6520ACBZ.pdf

(12 pages)

Specifications of ISL6520ACBZA

Pwm Type

Voltage Mode

Number Of Outputs

1

Frequency - Max

340kHz

Duty Cycle

100%

Voltage - Supply

4.5 V ~ 5.5 V

Buck

Yes

Boost

No

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

8-SOIC (3.9mm Width)

Frequency-max

340kHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Compensation Break Frequency Equations

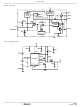

Figure 6 shows an asymptotic plot of the DC/DC converter’s

gain vs frequency. The actual Modulator Gain has a high gain

peak due to the high Q factor of the output filter and is not

shown in Figure 6. Using the previously mentioned guidelines

should give a Compensation Gain similar to the curve plotted.

The open loop error amplifier gain bounds the compensation

gain. Check the compensation gain at F

capabilities of the error amplifier. The Closed Loop Gain is

constructed on the graph of Figure 6 by adding the Modulator

Gain (in dB) to the Compensation Gain (in dB). This is

equivalent to multiplying the modulator transfer function to the

compensation transfer function and plotting the gain.

The compensation gain uses external impedance networks

Z

loop. A stable control loop has a gain crossing with

-20dB/decade slope and a phase margin greater than 45

degrees. Include worst case component variations when

determining phase margin.

Component Selection Guidelines

Output Capacitor Selection

An output capacitor is required to filter the output and supply

the load transient current. The filtering requirements are a

function of the switching frequency and the ripple current.

The load transient requirements are a function of the slew

rate (di/dt) and the magnitude of the transient load current.

F

F

4. Place 1

5. Place 2

6. Check Gain against Error Amplifier’s Open-Loop Gain.

7. Estimate Phase Margin - Repeat if Necessary.

FIGURE 6. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

FB

Z1

Z2

100

-20

-40

-60

80

60

40

20

0

and Z

=

=

----------------------------------- -

2π x R

------------------------------------------------------ -

2π x R

10

20LOG

(R

2

MODULATOR

IN

/R

ST

ND

(

1

1

to provide a stable, high bandwidth (BW) overall

)

GAIN

2

100

1

Pole at the ESR Zero.

Pole at Half the Switching Frequency.

x C

1

+

R

1

3

) x C

1K

F

Z1

F

FREQUENCY (Hz)

3

LC

F

Z2

10K

F

F

8

F

P1

P2

F

P1

ESR

(V

=

=

100K

IN

20LOG

F

-------------------------------------------------------- -

2π x R

----------------------------------- -

2π x R

/DV

P2

P2

OSC

OPEN LOOP

ERROR AMP GAIN

1

with the

1M

2

3

)

x

x C

1

COMPENSATION

⎛

⎜

⎝

CLOSED LOOP

C

--------------------- -

C

3

1

1

10M

GAIN

x C

+

GAIN

C

2

2

(EQ. 5)

⎞

⎟

⎠

ISL6520A

These requirements are generally met with a mix of

capacitors and careful layout.

Modern components and loads are capable of producing

transient load rates above 1A/ns. High frequency capacitors

initially supply the transient and slow the current load rate

seen by the bulk capacitors. The bulk filter capacitor values

are generally determined by the ESR (Effective Series

Resistance) and voltage rating requirements rather than

actual capacitance requirements.

High frequency decoupling capacitors should be placed as

close to the power pins of the load as physically possible. Be

careful not to add inductance in the circuit board wiring that

could cancel the usefulness of these low inductance

components. Consult with the manufacturer of the load on

specific decoupling requirements.

Use only specialized low-ESR capacitors intended for

switching-regulator applications for the bulk capacitors. The

bulk capacitor’s ESR will determine the output ripple voltage

and the initial voltage drop after a high slew-rate transient. An

aluminum electrolytic capacitor’s ESR value is related to the

case size with lower ESR available in larger case sizes.

However, the Equivalent Series Inductance (ESL) of these

capacitors increases with case size and can reduce the

usefulness of the capacitor to high slew-rate transient loading.

Unfortunately, ESL is not a specified parameter. Work with

your capacitor supplier and measure the capacitor’s

impedance with frequency to select a suitable component. In

most cases, multiple electrolytic capacitors of small case size

perform better than a single large case capacitor.

Output Inductor Selection

The output inductor is selected to meet the output voltage

ripple requirements and minimize the converter’s response

time to the load transient. The inductor value determines the

converter’s ripple current and the ripple voltage is a function

of the ripple current. The ripple voltage and current are

approximated by the following equations:

Increasing the value of inductance reduces the ripple current

and voltage. However, the large inductance values reduce

the converter’s response time to a load transient.

One of the parameters limiting the converter’s response to

a load transient is the time required to change the inductor

current. Given a sufficiently fast control loop design, the

ISL6520A will provide either 0% or 100% duty cycle in

response to a load transient. The response time is the time

required to slew the inductor current from an initial current

value to the transient current level. During this interval the

difference between the inductor current and the transient

current level must be supplied by the output capacitor.

Minimizing the response time can minimize the output

capacitance required.

ΔI =

V

IN

Fs x L

- V

OUT

x

V

V

OUT

IN

ΔV

OUT

= ΔI x ESR

December 10, 2009

FN9016.6

(EQ. 6)