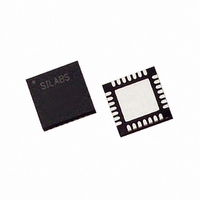

C8051F311-GM Silicon Laboratories Inc, C8051F311-GM Datasheet - Page 167

C8051F311-GM

Manufacturer Part Number

C8051F311-GM

Description

IC 8051 MCU 16K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F31xr

Datasheets

1.C8051F310-TB.pdf

(228 pages)

2.C8051F311-GM.pdf

(2 pages)

3.C8051F310-GQ.pdf

(218 pages)

Specifications of C8051F311-GM

Program Memory Type

FLASH

Program Memory Size

16KB (16K x 8)

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

I2C, SMBus, SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

25

Number Of Timers

4 bit

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F310DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 17 Channel

No. Of I/o's

25

Ram Memory Size

1280Byte

Cpu Speed

25MHz

No. Of Timers

4

Rohs Compliant

Yes

Package

24QFN EP

Device Core

8051

Family Name

C8051F31x

Maximum Speed

25 MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1446 - ADAPTER PROGRAM TOOLSTICK F311336-1253 - DEV KIT FOR C8051F310/F311

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1254

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

C8051F311-GM

Manufacturer:

SILICONLABS/芯科

Quantity:

20 000

Part Number:

C8051F311-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

15.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more

slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or

more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte

in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is

received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address

byte has been received. In the UART interrupt handler, software will compare the received address with

the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable

interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0

bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the

data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmis-

sions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple

slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master

processor can be configured to receive all transmissions or a protocol can be implemented such that the

master/slave role is temporarily reversed to enable half-duplex transmission between the original master

and slave(s).

Figure 15.6. UART Multi-Processor Mode Interconnect Diagram

RX

Master

Device

TX

RX

Device

Slave

TX

Rev. 1.7

RX

Device

Slave

C8051F310/1/2/3/4/5/6/7

TX

RX

Device

Slave

TX

V+

167