HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 11

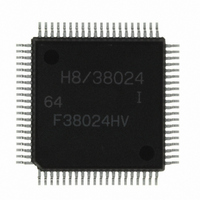

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Section 1

1.1

1.2

1.3

Section 2

2.1

2.2

Overview...........................................................................................................................

1.1.1

1.1.2

1.1.3

1.1.4

Registers............................................................................................................................

1.2.1

1.2.2

1.2.3

Instructions........................................................................................................................

1.3.1

1.3.2

1.3.3

1.3.4

Explanation Format........................................................................................................... 31

Instructions........................................................................................................................ 36

2.2.1 (1)

2.2.1 (2)

2.2.2

2.2.3

2.2.4

2.2.5

2.2.6

2.2.7

2.2.8

2.2.9

2.2.10

2.2.11

2.2.12

2.2.13

2.2.14

2.2.15

2.2.16

2.2.17

CPU

Instruction Set

Features .............................................................................................................

Data Structure ...................................................................................................

Address Space...................................................................................................

Register Configuration......................................................................................

General Registers ..............................................................................................

Control Registers ..............................................................................................

Initial Register Values.......................................................................................

Types of Instructions.........................................................................................

Instruction Functions.........................................................................................

Basic Instruction Formats ................................................................................. 20

Addressing Modes and Effective Address Calculation ..................................... 26

ADD (add binary) (byte) ................................................................................. 36

ADD (add binary) (word)................................................................................ 37

ANDC (AND control register) ........................................................................ 41

BAND (bit AND) ............................................................................................ 42

Bcc (branch conditionally) .............................................................................. 43

BCLR (bit clear).............................................................................................. 46

BIAND (bit invert AND) ................................................................................ 47

ADDS (add with sign extension)..................................................................... 38

ADDX (add with extend carry) ....................................................................... 39

AND (AND logical) ........................................................................................ 40

BILD (bit invert load) ..................................................................................... 48

BIOR (bit invert inclusive OR) ....................................................................... 49

BIST (bit invert store) ..................................................................................... 50

BIXOR (bit invert exclusive OR).................................................................... 51

BLD (bit load) ................................................................................................. 52

BNOT (bit NOT)............................................................................................. 53

BOR (bit inclusive OR)................................................................................... 54

BSET (bit set).................................................................................................. 55

....................................................................................................................

................................................................................................. 31

Contents

Rev. 2.00 Dec 27, 2004 page ix of xii

1

1

1

2

5

5

6

6

6

7

8

8

9