HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 20

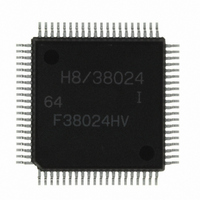

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 20 of 145

- Download datasheet (2Mb)

Section 1 CPU

1.2

1.2.1

All the general registers can be used as both data registers and address registers. When used as

address registers, the general registers are accessed as 16-bit registers (R0 to R7). When used as

data registers, they can be accessed as 16-bit registers (R0 to R7), or the high (R0H to R7H) and

low (R0L to R7L) bytes can be accessed separately as 8-bit registers. The register length is

determined by the instruction.

R7 also functions as the stack pointer, used implicitly by hardware in processing interrupts and

subroutine calls. In assembly language, the letters SP can be coded as a synonym for R7. As

indicated in figure 1-4, R7 (SP) points to the top of the stack.

1.2.2

The CPU has a 16-bit program counter (PC) and an 8-bit condition code register (CCR).

(1) Program Counter (PC): This 16-bit register indicates the address of the next instruction the

CPU will execute. Instructions are fetched by 16-bit (word) access, so the least significant bit of

the PC is ignored (always regarded as 0).

(2) Condition Code Register (CCR): This 8-bit register indicates the internal status of the CPU

with an interrupt mask (I) bit and five flag bits: half-carry (H), negative (N), zero (Z), overflow

(V), and carry (C) flags. The two unused bits are available to the user. The bit configuration of the

condition code register is shown below.

Rev. 2.00 Dec 27, 2004 page 6 of 128

REJ09B0214-0200

Registers

General Registers

Control Registers

SP (R7)

Figure 1-4 Stack Pointer

Unused area

Stack area

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: