HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 21

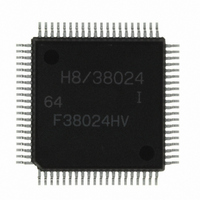

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

*

Bit 7—Interrupt Mask Bit (I): When this bit is set to 1, all interrupts except NMI are masked.

This bit is set to 1 automatically at the start of interrupt handling.

Bits 6 and 4—User Bits (U): These bits can be written and read by software for its own purposes

using LDC, STC, ANDC, ORC, and XORC instructions.

Bit 5—Half-Carry (H): This bit is used by add, subtract, and compare instructions to indicate a

borrow or carry out of bit 3 or bit 11. It is referenced by the decimal adjust instructions.

Bit 3—Negative (N): This bit indicates the value of the most significant bit (sign bit) of the result

of an instruction.

Bit 2—Zero (Z): This bit is set to 1 to indicate a zero result and cleared to 0 to indicate a nonzero

result.

Bit 1—Overflow (V): This bit is set to 1 when an arithmetic overflow occurs, and cleared to 0 at

other times.

Bit 0—Carry (C): This bit is used by:

Note that some instructions involve no flag changes. The flag operations with each instruction are

indicated in the individual instruction descriptions that follow in section 2, Instruction Set. CCR is

used by LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used by

the conditional branch instruction (Bcc).

1.2.3

When the CPU is reset, the program counter (PC) is loaded from the vector table and the interrupt

mask bit (I) in CCR is set to 1. The other CCR bits and the general registers are not initialized.

Bit

Initial value

Read/Write

Add, subtract, and compare instructions, to indicate a carry or borrow at the most significant

bit

Shift and rotate instructions, to store the value shifted out of the most or least significant bit

Bit manipulation instructions, as a bit accumulator

Not fixed

Initial Register Values

R/W

7

*

I

R/W

U

6

*

R/W

H

5

*

R/W

U

4

*

Rev. 2.00 Dec 27, 2004 page 7 of 128

R/W

N

3

*

R/W

Z

2

*

REJ09B0214-0200

R/W

V

1

*

Section 1 CPU

R/W

C

0

*